insert_stdcell_filler试图在有stdcell的地方插filler后报错

结果报 cannot satisfy min width rule at (44.772 51.504)

请问什么原因会导致insert_stdcell_filler会在有cell的地方插filler?

会不会是坐标报错了呢

legalizer_consider_vth_spacing 与insert_stdcell_filler有什么关系?

vth rule在哪里定义的?

报错的坐标位置是两个紧贴的cell,一个是HIVT的一个是LOVT的,

将报错坐标上的HIVT cell 换成LOVT的后,不会试图在那个位置插入filler并报错了。

但是根本原因是什么呢?

为什么命令会试图在那个地方插入filler?

有没有大神解答一下。

什么工艺什么库,有点奇怪的

标题

gf14,很是奇怪啊,一个星期了都还没解决

标题

经试验,将legalizer_consider_vth_spacing关了或者将HIVT cell换成LOVT的就不会在那里插filler了,应该是vth rule的问题,可还是不知怎么解决

太先进了表示没有玩过,没法解释

解决:这里并不是想在此处插filler,而是报这个位置不满足VT的minWidth

发信给 solvnet 请求解决下,

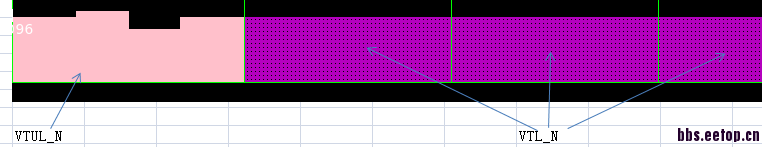

你好,你的问题解决了吗?目前我也遇到到了相同的问题,tsmc16nm工艺,两个不同的VT之间本来不需要插入filler(ULVT和LVT),但是工具报这个地方Error: cannot satisfy min width rule at (0.52, 0). (APL-095).按照你帖子里面的把set legalizer_consider_vth_spacing false设置为false,结果是Error: cannot satisfy min width rule at (0, 0). (APL-095),很困惑,盼回复

这是因为16nm的工艺有advance rule,你要挪std cell

谢谢你的回复,在check_lega的时候的确有这样的warning:Warning: There is an "Advanced Technology Rule" violation with cell xxxx (DPI-059),请问下这样的warning是什么意思?没有搞太清楚,如果要fix的话如何fix呢?目前design采用manual place。

另外你说的需要挪cell,是从哪方面考虑?

谢谢

注意OD和VT的问题

能说的具体点吗? 个人理解主要针对width< 2*pitch or 3*pitch 的invd0、bufd0之类的cell考虑vt和OD的area,但在icc中报的advanced technology rule好像不是在这些cell上。报warning的这些cell VT和OD都没有问题

你看一下tech file, 找到 LAYER ULVT和 LAYER LVT, 里面有min width 和min spacing的定义, 同一种vt的cells的宽度不能小于tf中定义的值。16nm工艺应该不能将

legalizer_consider_vth_spacing设置为false, 你可以将其他vt的cell挪开一点。

为什么你设为false还是报错那就不理解了。

谢谢你的回复,tf里面关于vt的min space和min width的value都是0.36。这个对不规则vt如何理解,比如现在用到“凹”形VT。如果看整个cell的vt,是满足条件的,如果仅仅看右边凸出的那部分,是小于0.36,这个没太搞明白。

标题

一般vt和cell的形状是一样的,你可以看一下lef。

那仅仅是通常情况下,想xor2、xor3的注入成都是不规则的。

如#19中图片所示,ULVT及LVTcell之间按理不应该插入filler,但是在insert filler的时候就报vt error,在此需要插入filler。把这两个cell放在virtuoso中单独check,发现没有vt方面的drc error。

没见过那样的,安全起见,还是插上filler

学习了