什么是High-Level Sythnesis Flow?

时间:10-02

整理:3721RD

点击:

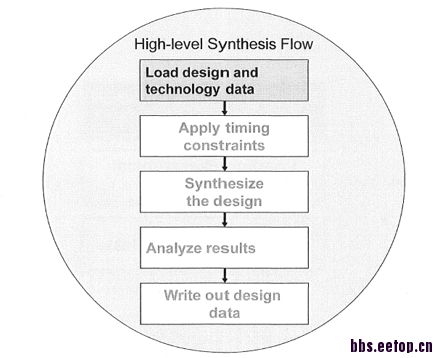

我们从RTL到GDS的过程也就属于High-Level Sythnesis Flow了?

同问,帮顶顶下

就是普通综合的意思

我也感觉是,但还有这么高端的名字,也是醉了。

没见过,坐等牛人

silicon compiler

cadence synergy

後出現 synopsys design compiler

rtl = verilog/VHDL

system C

synopsys 分rtl design compiler , 和更高階 behavior compiler

只有聽說過behavior compiler

C synthesis tools

FROM WIKI

- bambu from Politecnico di Milano (Italy) with free source code at PandA framework website

- BlueSpec Compiler from Bluespec, Inc.

- HLS-QSP from CircuitSutra Technologies

- C-to-Silicon from Cadence Design Systems

- Concurrent Acceleration from Concurrent EDA

- Synphony C Compiler from Synopsys

- PowerOpt from ChipVision

- Cynthesizer from Forte Design Systems, acquired by Cadence Design Systems on 2014, February 14th

- Catapult C from Calypto Design Systems

- CyberWorkBench from NEC

- C-to-Verilog from C-to-Verilog.com

- C2R from CebaTech

- CoDeveloper from Impulse Accelerated Technologies

- eXCite from Y Explorations

- GAUT From Universite de Bretagne Sud/Lab-STICC

- HercuLeS commercialized and marketed by Ajax Compilers

- LegUp from University of Toronto

- PICO from Synfora, acquired by Synopsys in June 2010 (PICO = Program In/Code Out)

- Shang

- Xilinx Vivado (formerly AutoPilot from AutoESL

- xPilot from University of California, Los Angeles

- Vsyn from

- ngDesign from SynFlow

- AUGH from TIMA Laboratory

- ROCCC

- PandA from Politecnico di Milano

Catapult C 應該比較長聽到吧