DFT的OCC流程的问题

时间:10-02

整理:3721RD

点击:

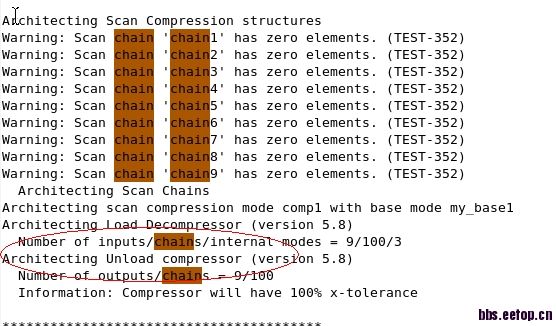

设计中,我自己写的OCC电路。在basic OCC模式下,根据preview_dft的报告扫描链正确,但是在压缩模式下,preview_dft的报告,扫描链不正确,而且内部扫描链的条数以及ScanDataIn Ports与ScanDataOut Ports与我定义的不匹配,工具自己创建了一些test_so*。

我定义的扫描链,在basic occ 下面是10 scan chain + 1个clk chain 共 11条。

我在compress occ 下面,定义了100条。 preview_dft报告出来是102条。

上面信息中,Number of inputs / outputs 是9,是不是不大正确啊?

/Catch1(10-14-15-(10-14-15-57-37).jpg)

压缩模式下只能定义压缩比吧, 可以定义具体压缩链的数量吗? 压缩比定义之后工具会自己生成压缩链的数量。 另外请问兄台, OCC的pattern你用tmax生成了吗? 我现在能用DC生成clock control 电路。但就是不能用tmax生成at speed test 的pattern. 只能生成pll bypass mode下的单一clock的pattern. 不知道tmax里该怎么设才能生成at speed test pattern.

我現在用DFTC 2012 insert scan 用SNPS OCC 生成電路並產生STIL(spf)。 Tetramax 2010吃進去STIL and scan-inserted verilog netlist. 但tmax 2010就是不能生成at speed test 的pattern. 只能生成pll bypass mode下的pattern.Synopsys flow 真是不好用...太差了.

我现在也是遇到同样的问题,TetraMax只产生occ_bypass mode的pattern。请问你的问题解决了么?如何解决的?是否和TetraMax版本有关?

感谢!

xuexixuexi

路过学习