求助,多电压设计的时候如何定义一个有两个power port的sram电源连接方式?

一个multivolage的设计在dc阶段的时候带上了sram。这个sram有两个power port,VDDCE和VDDPE。但只有一个ground port VSSE。

按照要求,两个power port实际是接上同样的电源。也没有power gating的问题。

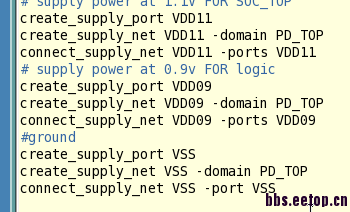

但是在MV的upf做定义的时候,应该如何定义这两个power在我定义的power domain里面怎么和create出来的power port连接呢?

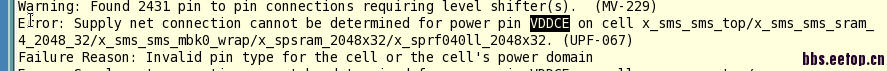

目前因为没有做这样的定义,dc阶段工具报告了如下的错误,认为有一个多出来的power port不知道要分什么样的电源给它。

补充一下,我的upf里面定义了两个power domain。PD_TOP是要放着sram的。

下图是定义的各个power domain的power port

用derive_pg_connections -cells -pins 吧, 这是死方法

可能vddce属于secondary power pin,因此不能自动被derive到, vddpe算default primary power pin,

或者看看.lib,vddce有pg_pin 描述么?

对,PR的时候就是设置一个derive pg connection,然后两个VDDPE VDDCE都connect到同样的VDD就可以了。

我遇到的问题是在逻辑综合的时候,因为设置了multivoltage,这个sram因为有两个电压port,DC工具就报错了。大概意思应该是说我没有设置过对VDDPE和VDDCE要和谁连接,估计就是差一个命令的问题。

connect_supply_net VDD11 -ports ${memory}/VDDCE可以这样写么,查下

这命令可以用,谢谢了。

请教下另外一个问题。

route_opt之后发现有一些线short掉了。short的原因就是这个地方的std cell有些些密集

remove net之后再接一个route_zrt_eco修起来没什么效果。因为cell的pin太难出了。

整个PR的区域没什么congestion的影响,还有好多地方没用上呢。工具好像就喜欢把cell都塞在一起的样子。place的时候我也特地修了下congestion。整个cell density也才0.5-0.6。有些地方才0.3.

这种问题一般怎么处理呢?

placer_max_cell_density_threshold 变量是不是写成0.8 了这种?

这个选项是控制cell 拥挤程度的,最好维持缺省的-1 ,

利用率不高 route肯定没问题的,就是些设置的问题

大致找到原因了。这些出drc的cell周围有一些fix 住的L2H的LVLU单元。fix这些单元是因为route之前做了一个preroute_standard_cell -mode nets,把cell的secondary power之类的接到strap和ring上了。然后route前加上了dont touch。

但是工具也不怎么聪明。陷在这些fix单元周围或者里面的其它单元貌似没法在route的阶段移动到其它区域。

可以手动在这块区域附近加soft blockage,控制这块区域的density,比如设置一个100u*100um的框,max density 设置为40%