place之后有detour现象,一般怎么处理呢

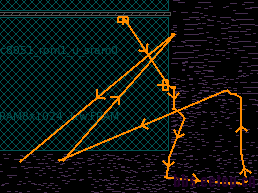

place阶段:这是reg2reg这组group中最差的一条path;感觉有点detour,利用什么命令或者什么方法能优化呢,试过

psynopt和place_opt -skip_initial_placement 效果不明显; 然后人工移动macro下侧的几个cell,但移动完之后,发现

slack更大;floorplan也做过三版了,觉得没啥可改的了!

是被macro挡住了, 摆放区域不够规整,可以调整下macro的位置么?

或者group_path -weight -critital_range 大些试试,

macro 四边附近加点hard soft place blockage,角上再多打1个hard place blockage 试试

恩 这个方法不错! 在macro四角落加一些!这样或许可以避免detour发生在macro的四角!

顺便请教下,如果是如下图所示这样,还有必要在macro四角加blockage吗

这是重新跑了一次place,在优化的时候做了些改动;虽然感觉不是很detour了;但slack并没有改变多少!

也用psynopt和groop_path -weight 跑过了,小编!

如果你highlight的是critical path的话 ,如果slack值不是很大的话 ,macro pin下翻转一下 ,如果很大的话,那要动fp了 ,或者place前, group 一些critical的path的cell ,move bounds 也好,直接place 这些reg都可以

多谢耐心回复,slack违例不是很大,1%的违例;

(1)macro pin翻转一下 ?这个您是指的将macro镜像吧,pin可以单独翻转?

(2) move bounds 还没用过;具体是将critical path上这些cell放大move bound中,然后再place?

Move the entire macro upside down, so pins will be facing the down side.

Signals from pin don't have to run a long distance to reach the next flop.

Try it.

icfbicfb had mentioned that already.

恩 多谢!

上图是我讲macro upside down之后得到的,没有镜像之前得到的会更更差一些!

我在macro的右上角和macro的底下一点地方,加入了soft placement blockage,然后place_opt之后,用了5次psynopt,得到了较好的结

果!

在这里说一下,并不是每次psynopt之后,时序都会变好!所以最好在每次psynopt之后,保存一下CEL,这样当下一次psynopt之后,如果时序

变坏,就直接采用上一次保存的CEL即可!

多玩玩积累些经验

psynopt还有这个鬼?回去试一下

1 对的 mirror2 理解正确