ICC的verify_drc失败,会是什么原因呢?

Jiancha检查选项 夹伤read cell view

选项夹伤是什么意思呢?我用了-read cell view了,第二个waring是没了,可是还是失败的,就不知道第一个waring所说的库不一致是什么概念?

要不试试verify_zrt_route吧

也有可能你没有hercules的license,或者你drc确实有问题?

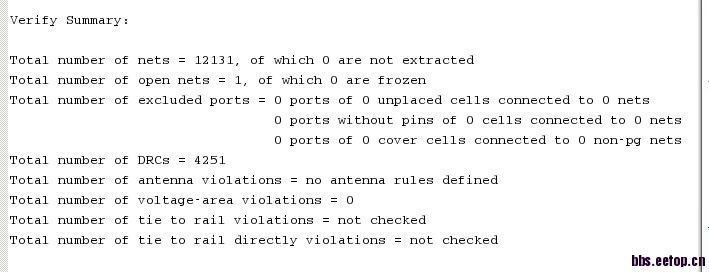

那就是可能因为我没装hercules,用verify_zrt_route去运行了下,结果说4251 nets违规。应该不会是这个问题吧?

如果你是用zroute来绕线的,那verify_zrt_route的结果就是真的。另外有一条线open了,也得仔细查查log。

恩恩。好像就是不太会利用那些自动生成的文件,里面的信息不太会去把握,真该去研究研究!

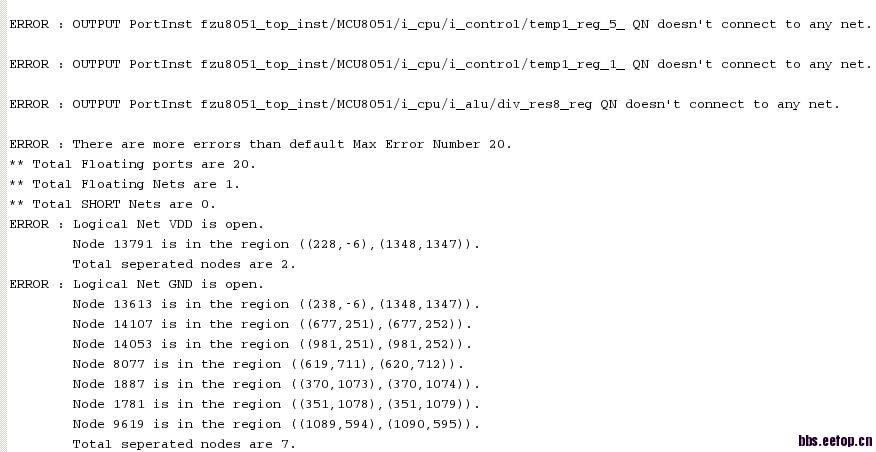

那个线违规的要怎么修复,里面就说了他违规了,貌似具体怎么说.那个开路的后来verify_lvs后,有说是电源地开路的,是一回事吗?

很明显没有hercules导致的问题

verify_zrt_route

route_zrt_eco

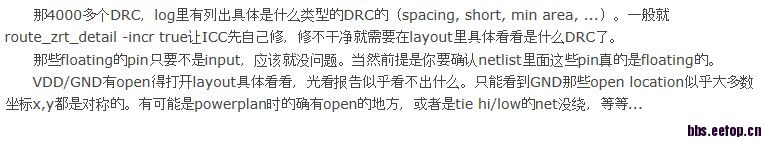

那4000多个DRC,log里有列出具体是什么类型的DRC的(spacing, short, min area, ...)。一般就route_zrt_detail -incr true让ICC先自己修,修不干净就需要在layout里具体看看是什么DRC了。

那些floating的pin只要不是input,应该就没问题。当然前提是你要确认netlist里面这些pin真的是floating的。

VDD/GND有open得打开layout具体看看,光看报告似乎看不出什么。只能看到GND那些open location似乎大多数坐标x,y都是对称的。有可能是powerplan时的确有open的地方,或者是tie hi/low的net没绕,等等...

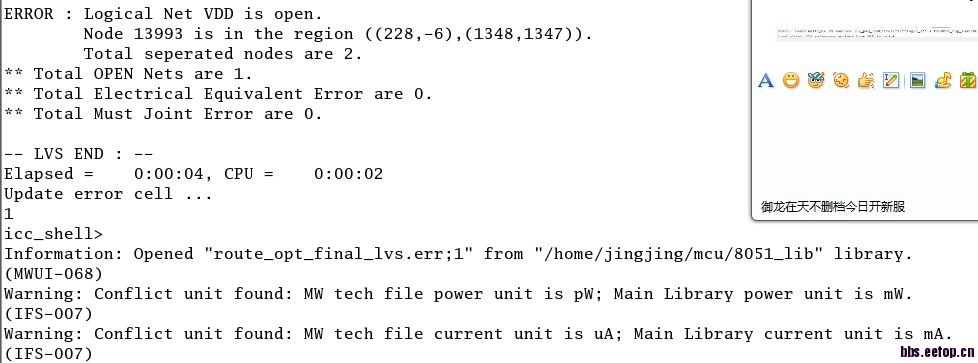

用route_zrt_eco修完后明显DRC就减少了,线违规变为两条,线open也没了,lvs里面的float也都剩下output的了。不过在LVS中还是有logical VDD是开路的,想说之前有用set_port_location 移动过VDD port的,貌似现在这个现在LVS也报说是float net,这会不会相互影响到呢?

我用了route_zrt_detail -incr true之后,是所有的DRC都修复了,但是LVS时的VDD逻辑开路,想请教下,在powerplant的时候有什么要注意的地方吗?我就知道说VDD/GND不要放在边角处,所以在放置的时候也就考虑了这一点。

derive_pg_connection了么?

恩。我再去运行了一下,重新verify_lvs,结果错误还是存在。

看之前你在verify_lvs时的报告,应该是打开-check_open_locator和-check_short_locator选项的吧。这样把lvs的结果load进ICC就能看到具体是什么地方报VDD open。

至于powerplan,这个话题比较大,一般还是先看user guide,多做做积累经验。

VDD/VSS的port随便放什么地方,只要搭到相应的VDD/VSS金属上就可以。

嘻嘻。谢谢你,耐心的、详尽、条理清晰的讲解和建议!

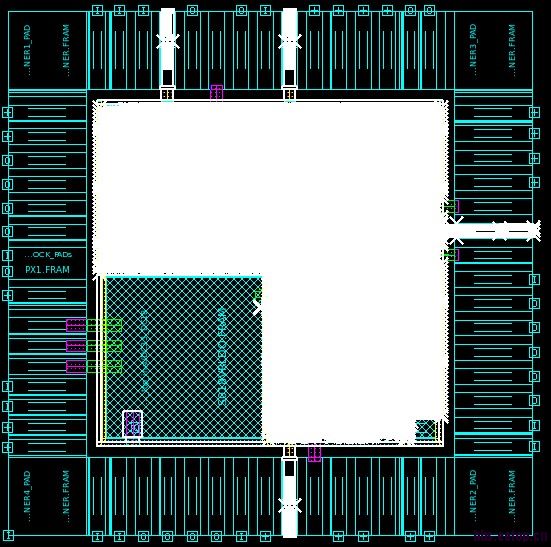

打开了,运行完后,我用error browser打开看,发现了只要是VDD连出来的地方都是,和core区域都是白茫茫的一片过去。

不知道你说的VDD的lvs open是什么样子?log给过来看看

一般来讲,只要接tiehi/lo的接对了,没有单元非法放置,那就没问题,最终calibre验证就可以了

那就随便找一个std cell的power pin看一下net_name的属性是不是你的power net的名字,如果是,你再看那个地方的power rail是不是power net。

还不行就逐一检查strape, ring, power pad pin conn吧~ 这个还是看具体layout才行~

也不知道截的这个信息对不。怎么看tiehi/lo是否接对,我就知道在synopsys_dc_setup里面有设置到tiehi/lo的而已。下面是版图上的图

好多白的xx呀,哈哈

做stripe了么?做rail了么?什么工艺呀?

.synopsys_dc_setup怎么设置的tiehi/lo呀?没有命令加tiehi/lo么?

我的是smic18的工艺,貌似有做过rail,不过没有加stripe,电源条一定要加的吗?

synopsys_dc_setup里面是这样设的set mw_logic0_net“GND”set mw_logic1_net "VDD",其他就没命令添加了,不懂得怎么添加,也不懂那个是干嘛用的说,跪求小编指教呀!

我怎么感觉似乎问题很严重的说!

看你的设计也不小呀,size是多少呀?

功耗多大?ring多宽?没有strips估计IR-drop会很大,反正不加有问题的概率比较大呗

你设置的部分不是TIEHI/LO,你只是指定了VDD/GND为逻辑1/0

http://bbs.eetop.cn/viewthread.php?tid=310078&highlight=

嘻嘻。记得好像做了rail了呀?不过我重新做的一遍,结果open就没了。

谢谢各位仁兄的大力帮助了!

我已经安装hercules在终端输入vue软件也启动了,然后在我ICC verfification 下拉菜单也有VUE选项,但是我还存在和小编一样的错误

icc_shell> verify_drc -read_cell_view

Warning: This command is no longer supported. Please use command signoff_drc instead.(RT-114)

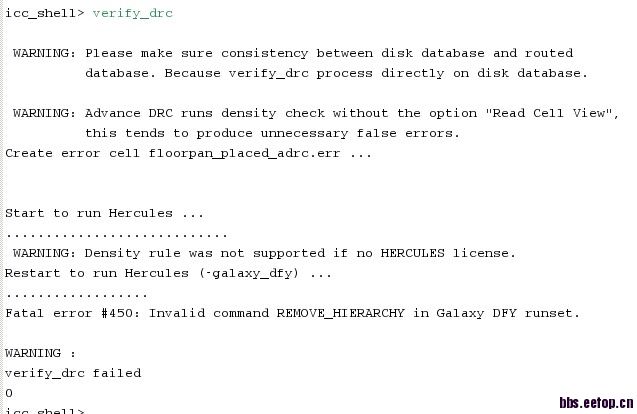

WARNING: Please make sure consistency between disk database and routed

database. Because verify_drc process directly on disk database.

Start to run Hercules ...

...................................

WARNING: Density rule was not supported if no HERCULES license.

Restart to run Hercules (-galaxy_dfy) ...

.........................

Fatal error #450: Invalid command REMOVE_HIERARCHY in Galaxy DFY runset.

WARNING :

verify_drc failed

0

版大 问个问题set_route_mode_options 这个命令可以打开或者关闭 zroute模式请问

set_route_options只能在没有打开zroute时的route_opt管用

set_route_zrt_detail_options是在打开zroute时的reoute_opt管用

verify_route和verify_zrt_route 的区别是什么呢 是不是如果再route时候用的是zroute模式,就用第二个;如果在route阶段用的不是zroute那么最后就用verify_route来检查呢