dft_drc 有error

时间:10-02

整理:3721RD

点击:

在电路中 插入occ后,tetramax里面执行dft_drc,结果报S1 violation.

trace 电路,发现是OCC产生的clock为X导致的。

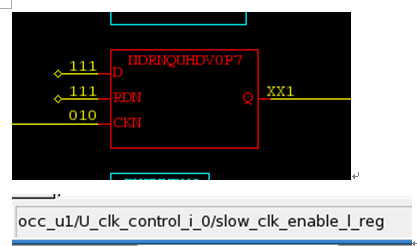

在往前trace,发现occ module里面,有一个DFF (fast_clk_enable)在shift mode检查时,

D pin为 111, CK为010, 此触发器为负延有效,在shift mode,Q端输出为XX1.

这个Q端的X值,经过右面的逻辑,传到触发器的CK就变成了CK为0X0, 就导致了S1 violation。

请问下,是否有人遇过同样的问题?该如何解决?

或者能否一起分析,讨论下?!

非常感谢!

trace到有问题的DFF截图如下:

希望多多帮忙~

难道就没有人遇过同样的问题么帮帮忙~

RE: dft_drc 有error【已解】

自己问,自己解吧~

之前只是在try flow,所以PLL的频率指定的比较低。

把PLL频率调高点儿,就不再报此问题了~