mask已出,如何在encounter中只对最上层的两层metal做ECO route ?

问一下, 我如果不想改动其他layer, 只对最上层的两层metal做ECO route, 可行吗?

刚改了一下tech lef,Design Import进来之后, 在NanoRoute里选ECO ROUTE, Frozen Metal ECO, 好像route没啥反应,

有没有哪位遇到过的,希望指点一下,谢谢

可以ecoroute啊, ecoroute -modify_only_layers top-1:top

我是这样做的,

1.Design Import时换用新的tech lef

2.restore design, 调入final design

3.去掉最上两层的filler, 然后ECORoute

完了以后好像没啥变化, 哪里不对吗?

最重要就是 ecoroute -modify_only_layers top-1:top ,

你确信新的techlef被正确load了么,如果前面load了老的techlef,后面的新的lef就被ignore了,

2.restore design, 调入final design

把你改的tech lef覆盖了吧

你可以读入新的lef,然后读最终的def,然后再eco

2.restore design, 调入final design

把你改的tech lef覆盖了吧

你可以读入新的lef,然后读最终的def,然后再eco

tech lef肯定是导入了,不过好像直接ecoRoute不行,

看了一下ecoRoute的说明, 说是必须先要ecoDefIn,

我就改了一下做法,

1.Design Import, 用新的tech lef, netlist用最后导出的.v

2.ecoDefIn, 实际上netlist和def是一样的,为了能进行ecoroute才做的

3.ecoroute -modifyonlylayers 5:6

然后route可以进行了, 不过......

route完了发现metal4怎么也被改动过了?

原来如此,谢谢

不过现在读入def进来做ecoroute,虽然设定了modifyonlylayers 5:6,

但metal4还是被改动了,不知道怎么回事?

算了, 用globaldetailroute 吧,

setNanorRouteMode-routeTopRoutingLayer 6 -routeBottomRoutingLayer 5

你确定你这个可行?

setNanoRouteMode -routeBottomRoutingLayer 5

setNanoRouteMode -routeTopRoutingLayer 6

globalDetailRoute

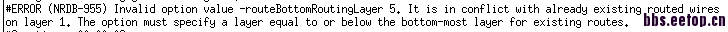

然后出现错误提示

不明白,定义的layer5 怎么会和layer1有冲突呢?

必须要设置等于或小于已经有的最底层的layer,这咋办啊?

那要分析下,m4是否不可避免的被修改掉。如果改动较大的话,被动到的概率还是挺大的

metal5利用率比较高,局部比较拥挤,

metal6整体改动,本来想metal5也跟着改的话差不多应该就可以了,

现在看来不行啊,metal4看上去动的还不少,

嗯嗯,改几层metal/via解决问题,还是基于设计本身吧。如果网表动的很少的话,那改动就是很少,否则,多动几层也是必然。

我的这个情况,网表没有任何改动的,

因为现在top metal加厚了,间距和宽度就不够了,所以要让top metal按照放大的尺寸重新route一下,

而且因为担心如果只改top metal的话,route会很困难,所以又把top-1 metal也放出来,允许改动,

没想到还是不行啊

ecoRoute 时,如何强制指定route layer,其他不指定的一律不动,即使route不过也不能动?

-modifyOnlylayer好像不怎么管用,还是会动到其他层,那样就不好控制了啊

setNanoRouteMode -routeEcoOnlyInLayers

这个可以吗,

请两位高手看看啊

呵呵,你有具体数据在手里,各种方案试一下就行了,单纯依靠经验判断没用。

单纯DRC不考虑timing影响的话

如果top metal的利用率不高,也许只改top metal width就可以了,它的加宽不会影响到已有的绕线的前提下。

如果加宽影响到已有绕线,metal需要动位置,那可以猜想top -1 metal也会动位置,因为top via的位置也会动;

top-1 metal的位置动了,并且利用率挺高的变动挺大的话,适当考虑,via和top-2的变动情况。

毕竟这个routing的congestion情况是不能泛泛讨论的,所以你就根据各个命令约束情况试一下就行了。

谢谢您的意见,呵呵

刚开始我也是认为top metal拉拉开距离,应该问题不大,最多top-1也跟着改一下,当然,via也是要动的,

不过可能局部太拥塞了,route不出来,好吧,那我就把top-2也放出来,

setNanoRouteMode -routeEcoOnlyInLayers 4:6

上面这个好像是强制性的

globalDetailRoute

这样错误少了很多,接近目标,

不过这样的话,要改5层layer,代价太高了啊

另外,东西面积比较小,单单改几层连线的话对timing影响不大的吧

还是重新RC抽取做PT验证的好,这样确保。是否对timing影响小,不同工艺节点,影响程度是不一样的

是啊,PT还是要跑一下的,

不过有问题的话,也只能有两三层metal可以动,办法不多啊,呵呵

按理说问题不大啊, 方便的话,数据发我下,我帮你试试,