encounter 里面CTS问题

时间:10-02

整理:3721RD

点击:

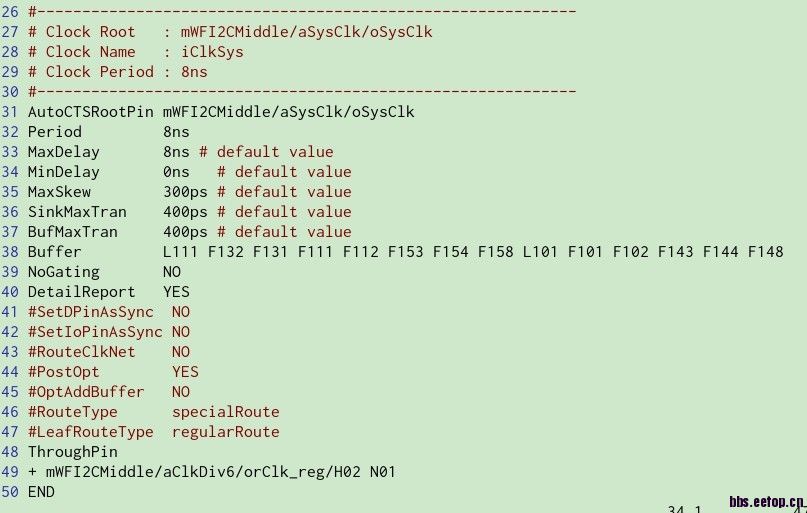

在设计中有两个时钟,一个是芯片内部时钟Sys_clk,一个是外部时钟Pad_clk,芯片一开始就通过一个选择器来选择哪个时钟(要么内部时钟工作,要么外部工作,不存在交互)。在做CTS的时候,一开始在create clk tree spc的时候产生ctstch文件中有两个时钟(Sys_clk和Pad_clk),如果直接把这个文件读入,是不是意味着encounter对整个芯片做一下Sys_clk的时钟树,然后再做下Pad_clk的时钟树?求解。

2个clock tree从选择器开始复用

在选择器后复用,这需要我们自己设定吗,还是CTS会自动做的? 我在sdc文件里面设置了set case analyze1 ,即恒定选择了外部clk作为芯片的时钟,我开始还以为在选择器之后是以外部clk来做时钟树的,与内部clk无关,看了下clk tree,内部clk貌似也有 clk tree。

CTS会自动做

那 设置了 Set case analyze 对那个时钟选择器做了选择,这句话对CTS会有影响吗?

你自己在#3不是已经回答了吗?

我开始以为这样设置后, encounter只会用外部CLK去做CTS,不管内部CLK。但实际上好像内部CLK也做了时钟树。我感觉这个设置好像没什么效果。

用实践去证明你的猜想,如果在工程有时间的情况下话.

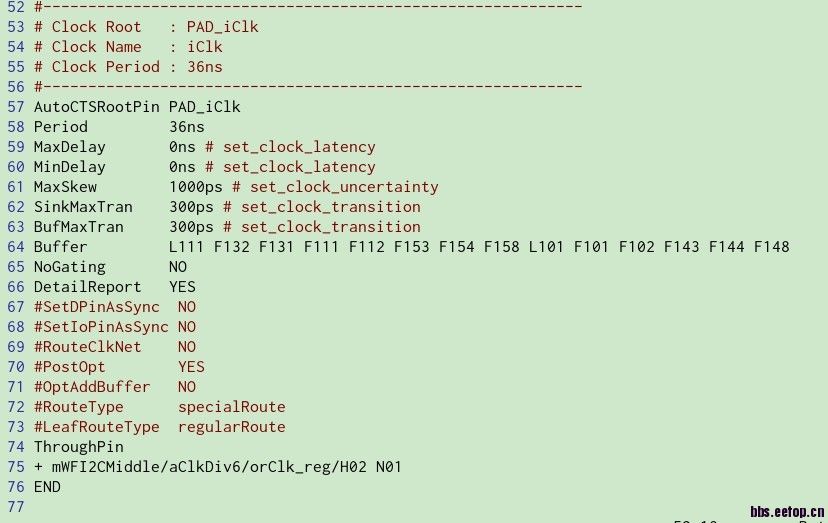

陈老大,再问下两个时钟(外部时钟和内部时钟,其中内部时钟经过6分频再和外部时钟做选择),看了ctstch文件上面有两个时钟,这样直接做cts可以吗?是不是还需要在选择器后面用一个generate clock。

mux之后做,

或者你改下spec, 留一个source也行的,自己试试就知道了

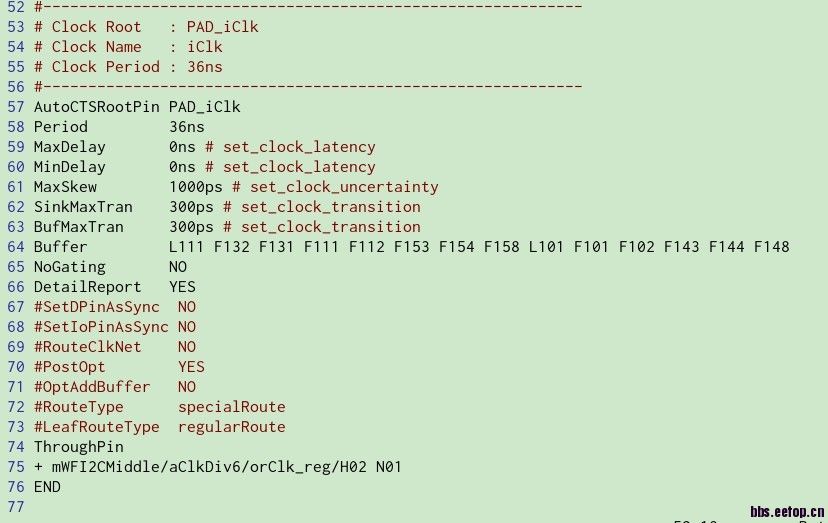

陈老大,我在用Encounter做CTS时,下面几个选项不知道怎么设置?我看许多人的Clock spec文件也都没有关注这几个参数,但是我发现Encounter会给出警告,工具貌似强烈希望对这几个参数进行设置。

#SetDPinAsSyncNO

#SetIoPinAsSync NO

#SetASyncSRPinAsSyncNO

#SetTriStEnPinAsSync NO