求助,primetime做postlayout时是否需要设置wire_load_model/mode?

时间:10-02

整理:3721RD

点击:

求助,

我看到很多参考脚本里面都有加上

set_wire_load_mode -top/enclosed

set_wire_load_model xxxxx

有个疑问,做postlayout的sta时,spef文件已经在pr过程后提取出来了,那么这个wire load的信息是否还需要?

我一直认为这个负载信息只是在综合的时候给dc估算延时用的,在pr的时候我就去掉了,在sta的时候也没加上。

我看到很多参考脚本里面都有加上

set_wire_load_mode -top/enclosed

set_wire_load_model xxxxx

有个疑问,做postlayout的sta时,spef文件已经在pr过程后提取出来了,那么这个wire load的信息是否还需要?

我一直认为这个负载信息只是在综合的时候给dc估算延时用的,在pr的时候我就去掉了,在sta的时候也没加上。

你的理解是对的。

反问你个问题,那两个命令用不同的组合去做综合,对综合出来的结果又哪些影响?

不同的线网模型(model)就会让dc计算rc的时候有不同的结果,至于mode我一直对top和enclose理解不深,大概就是继承上级或下级模块的线载属性吧。

那么,sta做postlayout是可以不要这两个约束了?可是我在用pt去report_wireload的时候。还是可以看到pt自动选择了wire_model,想问问这是怎么回事?

WLM是给tool来根据 fanin fanout来估计net delay的。

在postlayout之后,有了spef文件,我们可以用这个东西来反标,这个时候就不需要WLM了。

我在pt做postlayout时,就是读入了spef文件,但是pt为何还会有这个wire_load的信息?

线负载模型的数值set_wire_load_model为10X10,以及线负载模式set_wire_load_mode为top或者enclosed或者segmented,有什么区别?

也就是说线负载模型和线负载模式有什么区别?对设计有什么影响?大神解释下

你好~请问你这个弄明白没,我也在研究PT的这个设置,有进展说说啊

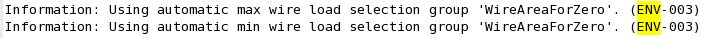

我也遇到了这个问题,PT提示了一个ENV-003的信息,大概是说PT自动选择了一个线负载模型。但是我读入了延迟信息文件啊