DFT插入 扫描链后 ,是用serial pattern进行仿真出错

时间:10-02

整理:3721RD

点击:

用 parallel pattern仿真无错,用serial pattern在第一个阶段,就是纯 scan in,然后 scan out阶段就出错了

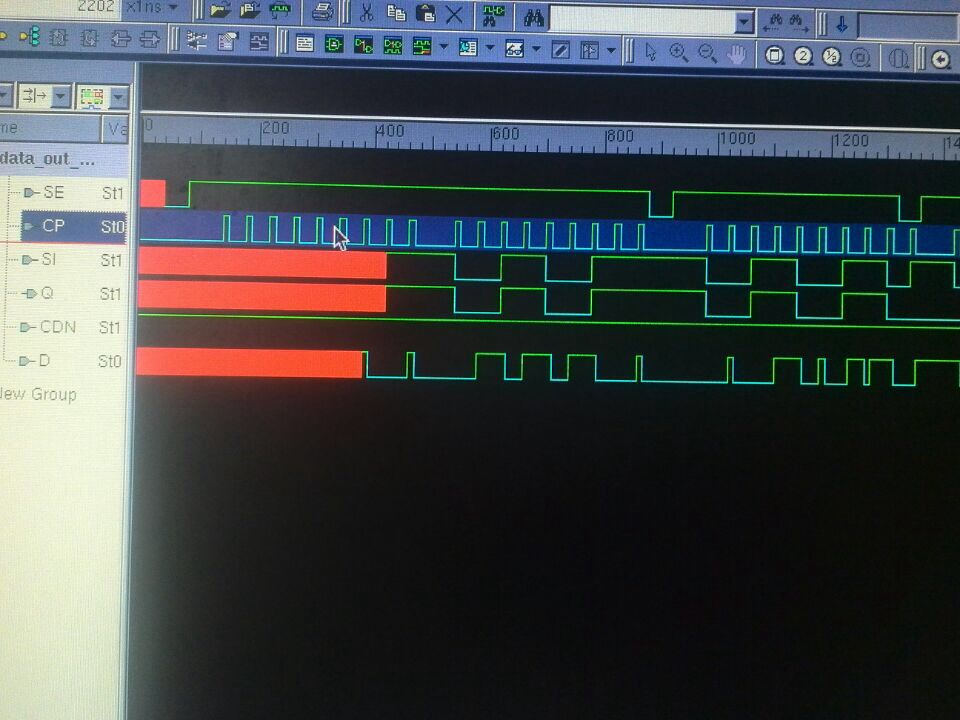

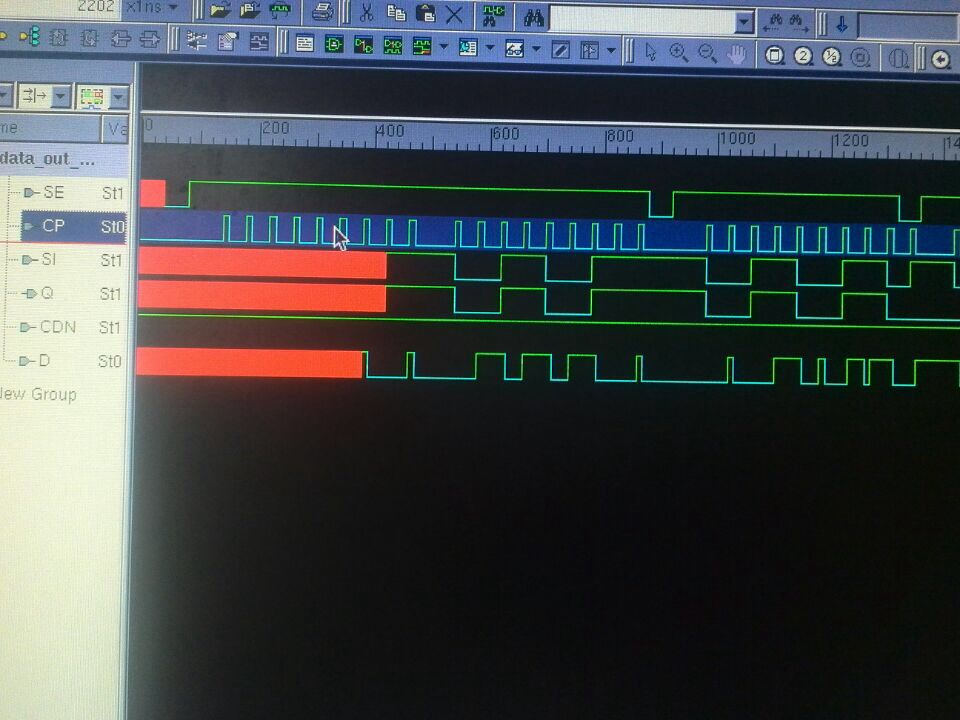

一级一级的往前倒着查,总算找到了出错的寄存器,出错原因如下图,发现中间有一个寄存器的功能不对了,输入和输出同时发生,成了buffer了。仿真是delay mode zero的。

另外,我发现只要插入了时钟门控的ICG cell后,扫描链就一定出现上面的情况,去掉就没有 。

然后始终报告内部有一个 non transparent latch。

搞了几天了,没解决这个问题,求助大家,谢谢了。

一级一级的往前倒着查,总算找到了出错的寄存器,出错原因如下图,发现中间有一个寄存器的功能不对了,输入和输出同时发生,成了buffer了。仿真是delay mode zero的。

另外,我发现只要插入了时钟门控的ICG cell后,扫描链就一定出现上面的情况,去掉就没有 。

然后始终报告内部有一个 non transparent latch。

搞了几天了,没解决这个问题,求助大家,谢谢了。

头大了一圈 ~·

serial 仿真经常出现timing的问题,你把触发器设成单位delay 比方说1ns,所有组合逻辑和clock gating都设成0 delay。

这是前仿的做法,如果后仿标入sdf就没有timing问题了若有可能就是time step设小点,当然前提是pt已经把hold修干净了。

ICG在test shift时,需要一直是时钟使能的状态。

好的,我明天试试,谢谢了

但是这个ICG不在扫描链上得哇,可是问题是只要他存在了,仿真就𣎴对了

谢谢了,用你的方法成功解决了困扰我的这个问题,拜谢 。