ICC中怎么实现special route?

在encounter中通过SRoute实现stdcell的p/g的连接

在ICC中,怎么操作实现呢?

刚开始学习,请达人帮忙

route_zrt_group

在preroute栏里,不过不是楼上说的那个。

多看看ug吧

derive_pg_connection -tie -power_net VDD_CORE

derive_pg_connection -power_net VDD_CORE

derive_pg_connection -tie -ground_net VSS_CORE

derive_pg_connection -ground_net VSS_CORE

fp_create_placement

preroute_standard_cells

先derive_pg_connection把所有的global net逻辑上连起来,然后再用preroute的命令来弄。

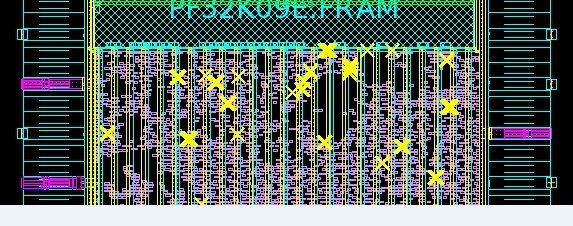

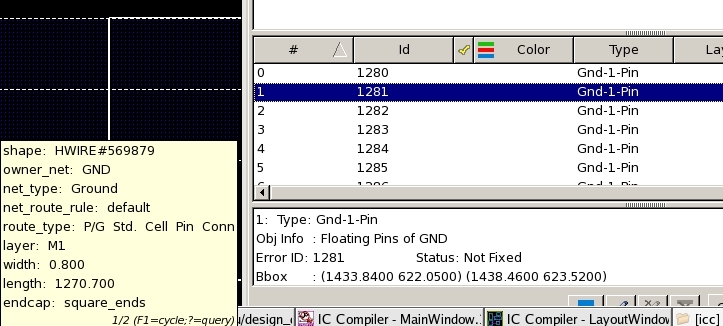

preroute_standard_cells 一定要在create_fp之后吗?我在之前做,貌似没加上的样子,后面布线之前,verify_pg_nets-rail 出现了很多floatpin都是在VDDGND上面。preroute_standard_cells -connect horizontal-do_not_route_over_macros-port_filter_mode off -cell_master_filter_mode off -cell_instance_filter_mode off -voltage_area_filter_mode off -route_type {P/G Std. Cell Pin Conn}

然后还做了竖直方向的strap,感觉错误在strap旁边,也不知道哪里出问题了。

preroute_standard_cells 一定要在create_fp之后吗?是的,出来形状了,才能做stdcell的special route。

preroute_standard_cells -fill_empty_rows -remove_floating_pieces

floorplan和powerplan做好了,没错误了,才开始后面的placement等工作,不然,白做。

恩恩,在create_fp_placemen和preroute_standard_cell后,有点小阻塞,然后我就设置了set_pnet_options -complete“M5 M6”不让标准单元防止在strap的下面,结果legalize_fp_placemen或重新create_fp_placement都出先了fail, 如果不设置,就不会出现fail了,不知道是不是我strap布得太密的缘故

那就不用complete,用partial试试

嘿嘿,用partical果然就不会出现fail的问题。

fp_create_placement

preroute_standard_cells后

verify_pg_nets的时候,log里面没有报VDD GND错误,但是到verification--》 errorbrowser里面rail出现了很多floatpin,

问题都是在std cell pin conn 、core ring和strap上面。

我strap 打竖直的方向,然后电源地分别用M5 M6 ,没有把奇偶层数分开,会不会影响到呢?

floating的vdd vss会不会是没有derive_pg_connection的原因造成的。

metal的走向遵循tf的规定比较好,你如果竖向既有M5又有M6,power阶段暂时没影响,但是routing的时候影响就出来了

我有derive_pg_connection ,估计没有每次添加电源网络都进行连接。

还有就是我DC综合的时候将VDD GND给去掉了,然后综合出来的网表,我没有在顶层添加VDD GND因为加完后会报错,不过我有derive_pg_connection ,有报连接上多少条,这个命令应该可以自动产生VDD GND ?

再请问下,网表中如果出现连接到逻辑0,1的能行吗?

网表中不需要出现VDD GND

出现1‘b0/1'b1正常,后面加TIEHI/TIELO单元就是了

恩恩,在您的提醒下,我去看了下tiehi和tielo单元的文档,貌似有时缺少这些单元还真的会引起DRCLVS错误,那我们一般在什么时候会选择添加这些单元呢?在刚导入设计的时候?

The Tie High (TIEHHD) and Tie low (TIELHD) Cells are used to tie off any

inputs to power or ground. The output of TIEHHD/TIELHD cell can provide

better ESD protection for internal cellswhen a cell input is isolated through

diffusion. DRC error or LVS short error may occur without these cells.

http://bbs.eetop.cn/viewthread.php?tid=310078&extra=&highlight=&page=1

嘿嘿,谢谢小编大人!