请教一个综合以及STA的mode选择问题

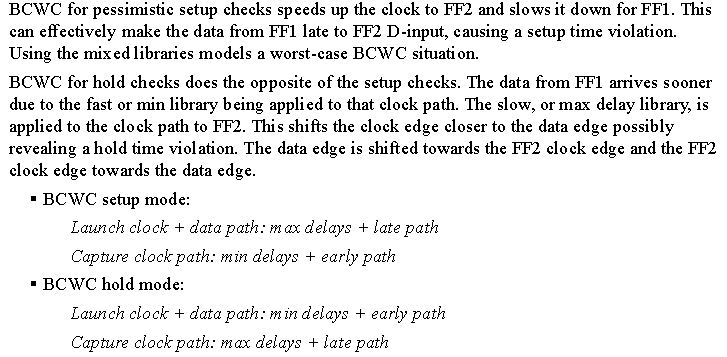

2。BCWC ANalysis mode, setup选max,hold选min

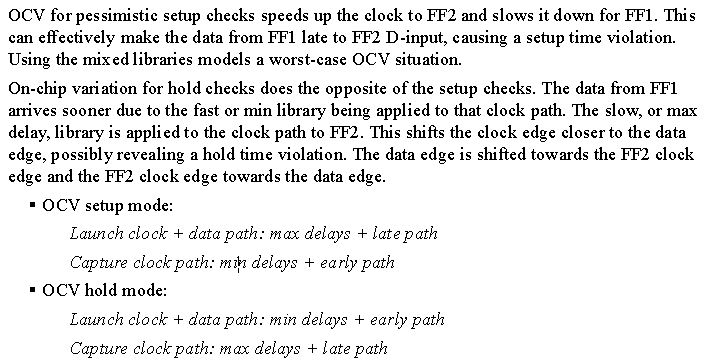

3, 另外就是On-chip variation

请教一下这里选择某种模式是不是完全取决于DC/RC综合的时候选择哪一种模式? 一般在综合的时候工程师是根据什么来决定选择哪种模式?(或者说,这三种模式都有哪些优点和缺点?)

没关系。ETS选哪个模式看芯片设计的需求。

一般根据芯片工艺和signoff的需求来选。例如65nm选BCWC,40nm就选OCV(只是个例子很多芯片不完全这样)。

谢谢小编的回复。

关于芯片的需求能举一些例子吗?是不是有些芯片应用于极端环境(比如高温),就需要更严格的timing。

看起来OCV优于BCWC优于Single,那OCV跟带timing derating的BCWC是不是一样的?感觉两者在max-min的选择上好像是相同的?

另外从设计需求的角度来看,他们怎么决定是不是BCWC就可以了,还是一定要min-max analysis? 是不是在分析逻辑得时候觉得担心slack不太够就用OCV来分析,觉得余量应该还蛮多,就BCWC就可以了?

OCV和BCWC本来就不一样,加上derate还是不一样啊。

你确定max-min的选择是一样的?

这两个有什么区别呢?

你赢了。

看来你对这wcbc和ocv理解那么透彻,那你说说它们的不同点。

我是不理解才问的,难道有很明显的不同我没看出来?

关于BCWC我的理解这是用于off-chip variation of delays, 比如说温度的影响,电压的影响。OCV意思很直接就是on-chip variation.

但是BCWC+Derating交换了min-max我就不理解了,所以才问一下小编,我哪里有理解错误。

关于BCWC我的理解这是用于off-chip variation of delays, 比如说温度的影响,电压的影响。OCV意思很直接就是on-chip variation.

但是BCWC+Derating交换了min-max我就不理解了,所以才问一下小编,我哪里有理解错误。

没见到过off-chip variation这个名词。意思倒是可以理解。看IP你是在法国登录,难道国外这些概念先进些。

我比较熟悉的是synopsys flow。cadence有没有这个概念就不知道了,麻烦joemool出来指明下。

你找些权威的资料,最好是cadence、synopsys、mentor等官方资料查看。

http://bbs.eetop.cn/thread-288486-1-1.html

http://bbs.eetop.cn/thread-284823-1-1.html

你先看看这两个帖子,里面有人传了个pdf文档,讲得挺详细的。

谢谢小编,我也是以前一直做DV,最近才接触这些东西,所以很多东西都只知道皮毛,我先看一下,我这个问题我去问问cadence吧,这些概念都是他们的讲义上的培训资料。(现在我有点怀疑他们写错了,想了半天,我觉得derating应该只是乘以一个系数0.8 or 1.1 etc..没有道理换max-min)

有什么结果我也可以过来给你共享一下:)

set_operating_conditions -analysis_type on_chip_variation \

-max slow -min slow

和

set_operating_conditions -analysis_type bc_wc \

-max slow -min slow

的静态时序的结果是一样的吗?

给AE打了个电话,他们说文档写错了:)

good