时钟综合问题

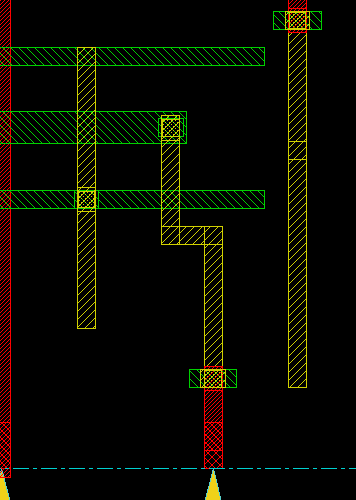

关于时钟树综合的问题,因为一般建议都是把时钟树上的走线都设为双倍线宽,双倍间距来着,我试着做了下,发现个问题,如下图所示

,从pin引出的线都是单倍的,只是都走了一小段之后才变为双倍的~

,从pin引出的线都是单倍的,只是都走了一小段之后才变为双倍的~问题是,pin输出的线都只有单倍,所以这条线上最大的耐流,其实也只是输出那段单倍线宽度乘以电流密度,,电流就是a,虽然后来加宽了,但是电流没变啊还是a,没起到双倍线可以增加耐流的作用啊?问问,我这样分析对吗?如果是对的,那么如何解决呢?

我认为双倍间距双倍宽度主要是从时序和信号完整性的角度来考虑的,靠近pin的地方做成一倍宽度是正常做法。当然也可以设置成PIN出来就是两倍宽度。

楼上正解!

我一直有疑问~请教下小编~

就是数字后端里面为什么对电流什么做很大关注啊~

难道不会有一个单元带不动后面几个单元的情况吗?比如就是电流太小的情况~

应该和信号王振兴有关系

没太明白你的问题是什么。如果担心驱动不够,那么看fanout和transition吧,如果驱动单元的驱动能力够了,那么它就能够驱动所带的单元,也就不会有transition的vio出现

实验室做模拟的就总不能理解数字里面fanout和transition,他们觉得驱动就是电流够不够,然后数字里面好像对电流大小不是特别关注,除了做power的时候~

数字信号非0即1(不定态X特例,不表)。数字设计人员考虑的是逻辑的实现和时序的实现,这种情况下,分析数字信号只能是看它是否翻转了,翻转的时间slew是否满足设计的要求,如果不能满足,那么上一级的驱动能力就不够。模拟信号可以输出中间电位,输出信号的精度等,两者设计人员的考虑点不同。当然,电路设计是互通的,模拟角度也可以进行数字电路的设计,也可以做仿真确认,然后分析。

由于数模设计的侧重点不同,数模部分的设计的分析方式也不同。对于数字设计STA分析,是不需要simulation的情况下,就能准确分析判断问题点的。当然power分析必须要有的,不然ir-drop也会影响到cell-delay和驱动的。而模拟设计,则需要不断地仿真,去确认设计的精度是否达到要求。

我上面也只是泛泛的点到为止,对于达到设计要求的是否改进算法和调整结构方面均不考虑,仅供参考。

对于后端来讲,数字考虑的不仅是floorplan的合理性,timing, congestion,power还要考虑工艺的影响和设计的要求等,很多东西,随着工艺节点的降低,SI和lowpower的设计也都有flow可供参考;模拟考虑的不仅是工艺的要求,更多的是设计的要求,包括精度匹配,噪声屏蔽,大功耗大电流设计等很多方面,也很杂。

总之,都是电路设计有相通的地方,但是要了解数模的差异和考虑分析问题的不同点。

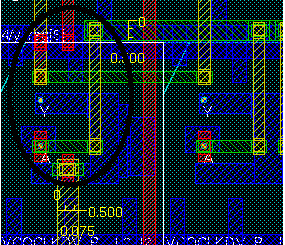

问下时钟树走线双倍宽度和间距地问题:

我在ctstch文件的参数设置如下:

RouteTypeNamespecialRoute

.....

PreferredExtraSpace2

end

.....

AutoCTSRootPinclk

....

RouteClkNetYES

RouteTypespecialRoute

end

但是时钟树综合完后看走线并没有达到想要的双倍线宽和间距,请帮看看问题出在哪?谢谢!

要在lef文件里面写一个special route的规则,要不你这special route在哪去找?

谢谢!难怪怎么找都找不到!

能不能给个基本格式?假设我时钟走线的层次是3 4层,基础的width 0.2 space 0.2

这个...我这台电脑上没有

其实你可以看encounter里面的help来查怎么做,里面是有的格式参考的

xiexie