ICC中执行route_zrt_detail之后存在DRC问题

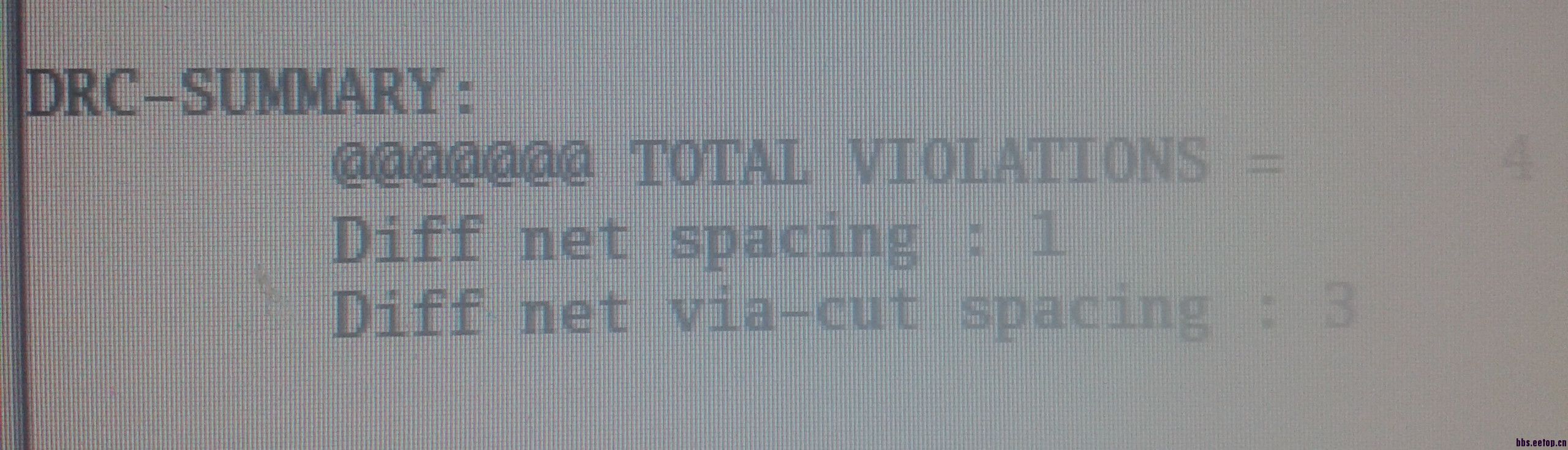

我在ICC中执行route_zrt_detail之后得到的报告如下图所示:

请问这个Diff net spacing和Diff net via-cut spacing是什么意思?

谢谢!

就是说的space不够吧,可以尝试route_zrt_eco

其实,这种情况不一定有问题,具体看版图的链接情况,导入到calibre下验证试试就知道了。

我可以这样理解吗?就是这种问题在ICC中可以忽略,到calibre中修,是吗?

谢谢!

我可以这样理解吗?就是这种问题在ICC中可以忽略,到calibre中修,是吗?

谢谢!

就这么几个,手修啦

是的,也许在calibre中也不是错,也没准,你试一下就知道了

如果是错,手动修正就可以啦

您说的手修是在calibre里面吗?ICC中可以弄吗?

谢谢!

我在calibre里面看了,是错误,有两百多个(因为每个通孔是阵列的形式,例如3X4,工具会报出4个错误)。不知道在ICC中能不能修?

谢谢!

via array的space不够?

那是tf文件有问题了吧。

几百个得让工具修。考虑改tf文件对应via的部分。

不是tf文件的问题,因为我有memory,它的外面一圈是电源地,而我做preroute_instances的时候也会在power/ground连接的地方或者附近打孔,这样就有重叠或者多余的孔,然后就存在这样的问题。不知道小编有什么建议?

谢谢!

不是tf文件的问题,因为我有memory,它的外面一圈是电源地,而我做preroute_instances的时候也会在power/ground连接的地方或者附近打孔,这样就有重叠或者多余的孔,然后就存在这样的问题。不知道小编有什么建议?

谢谢!

“memory,它的外面一圈是电源地” 这个是你自己加的还是自带的?

如果自己加的话,我觉得,你可以采用比较top的metal去做,可能好点吧。

如果自带的,那加stripe的时候连过去就可以了。

一般来说有孔的地方,工具会识别并躲避的,不会给重叠加的。

提供一个修改意见供参考

如果做preroute_instances 出来的孔是多余的,供电没问题的话,可以自己写个简单脚本将caliber的违例报告中的坐标附近的孔在icc里选中删除,一了百了。如果两种孔属性无差,不能单独挑出来,可以先全删了,再重新补strape上的孔。感觉icc里面打多孔的时候是会出现无法识别孔间距的问题,DRC过不了

您的方法挺不错的,不知道这么脚本该怎么写?

非常谢谢!

memory外面一圈电源地是自带的,我在ICC中执行preroute_instances的时候会在连接的附近产生多余的孔。

谢谢!

请问后来是怎么解决的?

还是在calibre里面解决的,就算后来在ICC里面没有报DRC问题了,在calibre里面还是有。

那在calibre里修改完 还会icc么?还是改完就算了?最后不是要出spef的咩

abstract view 没有抓 via 出来,那 preroute instances 的时候又穿过同一个 pin 两层 metal 交接的地方,那就会自动打上 via 了。

可以试着修改 preroute instances 的 option, 或者先加上 blockage。

应该人手去删也不算麻烦吧,反正ICC里面也可以把 Calibre 的结果读进去,也可以把所有 violations hilight 出来

谢谢您提的方法,我可以再试试。您说的把calibre里面修改好的导回ICC,怎么弄?

非常感谢!

就没有回ICC改了,因为最后交出去的就是gds文件。但是我觉得这样不好,希望大侠能教教怎么导回ICC?

哈哈~!

就是因为回不去了 所以我改drc都是在icc里面对应着calibre报的坐标改 各种头大...

不是有个 DRC RESULTS DATABASE 吗

To convert the Calibre DRC error file to a Milkyway error view, use the read_drc_error_file command (or choose Verification > Read Third-party DRC Error File in the GUI).

啊啊啊啊啊 还可以这样!内牛满面!跪谢 赶紧试试去