icc shorts过多

时间:10-02

整理:3721RD

点击:

用verify_lvs -max_error 5000 -check_short_locator -error_cell verify.err跑出来4k多个shorts。

其中M5 & M6最多,都是1k多,部分是VDD/GND和信号线的短接。(TOP METAL为M6,面积7*7)

M1有100+,有信号线的短接,但是大部分还是VDD/GND和信号线的短接。

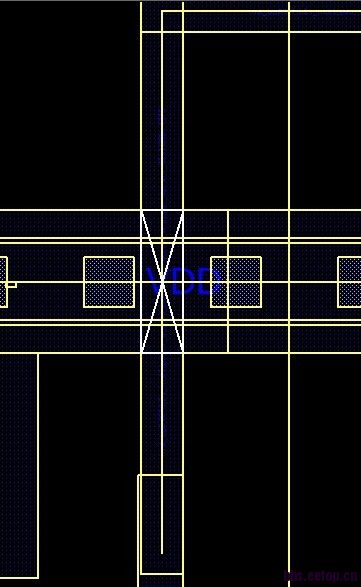

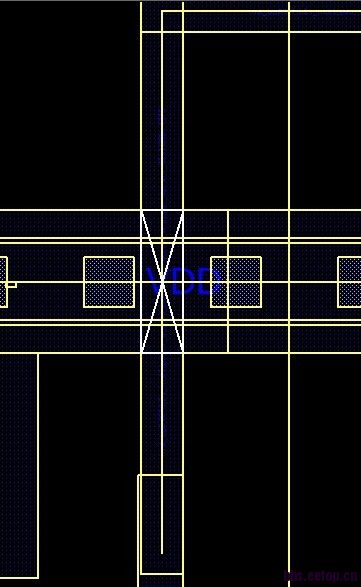

例如

其中M5 & M6最多,都是1k多,部分是VDD/GND和信号线的短接。(TOP METAL为M6,面积7*7)

M1有100+,有信号线的短接,但是大部分还是VDD/GND和信号线的短接。

例如

我现在routing的步骤是先做preroute,然后是clock net,然后是route_opt。

这个除了手工改以外有办法干预吗?是不是脚本里我缺少option?

请大侠指教啊~我现在是手工删了short的线再做route_zrt_eco,删线的工作量也是巨大。总觉得有办法可以工具处理的吧?

目前用的脚本如下:

route_zrt_group -all_clock_nets -reuse_existing_global_route true

optimize_clock_tree -routed_clock_stage detail -buffer_sizing -gate_sizing

route_opt -initial_route_only

route_opt -skip_initial_route -effort high

focal_opt -power -effort high

求教!

解决short是 route问题的重点,要看你design的, 具体要看数据的,一时半会说不清

看design看数据?能说的具体一点不?头一回做PR 也头一回看到这么多short 手工改的头都大了

看着怎么觉得像route后改变了power mesh呢

敢问 power mesh是啥。看到UG里好像有写到power mesh、、不过不太理解。 我脚本里哪条是更改这个的?不太懂~

请问后来怎么解决了啊

我在次高层纵向的strap下都放了cell 最后全设定不让放 cell的出Pin 就没问题了

请问楼上用了几层Metal,如果摆放率很高的话,岂不很难绕线?谢谢