数字后端求教

时间:10-02

整理:3721RD

点击:

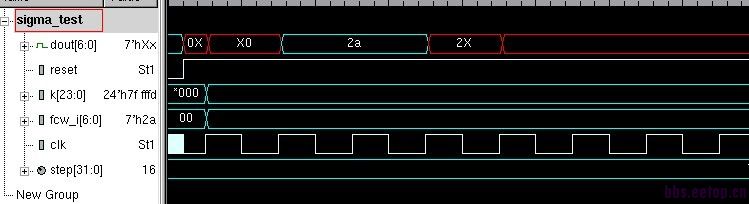

小弟在跑数字ASIC流程,用到DC,encounter,VCS软件。程序的前仿真时钟为20M波形如下

图一

(1)波形可以看出代码功能是正确的。

(1)波形可以看出代码功能是正确的。

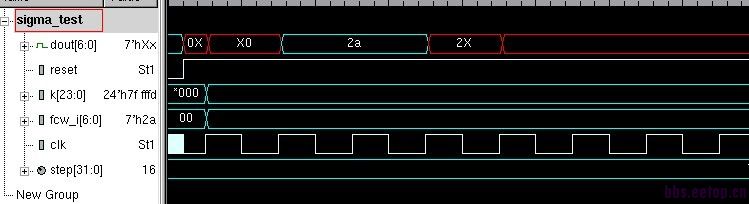

(2)然后用DC综合,综合脚本中用的是20M时钟进行设置,没有setup时序违例,读出此时的sigma.sdc和网表。但是发现问题①DC出来的网表用vcs仿真时,只能在10M的频率下工作,不能在20M频率下工作。下图为DC的网表在20M频率下的仿真图:

图二

(3)用encounter布局布线,其中的.sdc文件为20M时DC综合读出来的文件;生成版图后导出网表sigma_sim.v和延时文件sigma.sdf用于后仿真。

(4)用VCS将延时文件加载进去,同样的,此网表sigma_sim.v只能在10M的频率下工作,不能在20M下工作。如图三。

图三

请问各位大侠:①为啥我DC综合时没有任何违例,holdtime也用set_fix_hold clk修复了。没报任何错误,为啥DC的网表仿真中就出现了几个对的数值,其他都是X,跟图一的前仿差那么大,而且在10M的时候才能有正常波形呢?

②encounter布局布线的过程中,读入的.sdc文件是20M的,我也查过时序,没有报告说hold违例,但为啥encounter读出来的网表也只能在10M下工作呢?而且貌似后仿真的波形并不是一一对应前仿真的波形,如图一跟图三的对比,图三的后仿真中前面部分出现了X,后面才正常。请问这叫后仿真过了吗?

请各位指点一下。多谢了。

图一

(1)波形可以看出代码功能是正确的。

(1)波形可以看出代码功能是正确的。(2)然后用DC综合,综合脚本中用的是20M时钟进行设置,没有setup时序违例,读出此时的sigma.sdc和网表。但是发现问题①DC出来的网表用vcs仿真时,只能在10M的频率下工作,不能在20M频率下工作。下图为DC的网表在20M频率下的仿真图:

图二

(3)用encounter布局布线,其中的.sdc文件为20M时DC综合读出来的文件;生成版图后导出网表sigma_sim.v和延时文件sigma.sdf用于后仿真。

(4)用VCS将延时文件加载进去,同样的,此网表sigma_sim.v只能在10M的频率下工作,不能在20M下工作。如图三。

图三

请问各位大侠:①为啥我DC综合时没有任何违例,holdtime也用set_fix_hold clk修复了。没报任何错误,为啥DC的网表仿真中就出现了几个对的数值,其他都是X,跟图一的前仿差那么大,而且在10M的时候才能有正常波形呢?

②encounter布局布线的过程中,读入的.sdc文件是20M的,我也查过时序,没有报告说hold违例,但为啥encounter读出来的网表也只能在10M下工作呢?而且貌似后仿真的波形并不是一一对应前仿真的波形,如图一跟图三的对比,图三的后仿真中前面部分出现了X,后面才正常。请问这叫后仿真过了吗?

请各位指点一下。多谢了。

小编有QQ么?加我QQ:4018749 详谈

LZ,

你要檢查是什麼原因導致你的DFF出現unknow狀態,

不是一直把頻率降低去試哪一個會過

通常只有學生會一直換頻率去試

然而真正的原因很多時候都是 非同步訊號 造成的unknow

呵呵,我找到原因了,是DC脚本写的有问题,重新设置参数,问题解决了。

能不能讲讲具体什么原因,以后其他人有类似的问题时,做个参考

小编,小弟惭愧,我在论坛先后发了两个差不多的帖子。DC综合后网表没有问题,而是我的测试代码写得有问题。http://bbs.eetop.cn/thread-400561-1-1.html这是第二个帖子,有高手指导了一下我的测试文件,结果就OK了。