问两个纠结的问题,请大家回答

时间:10-02

整理:3721RD

点击:

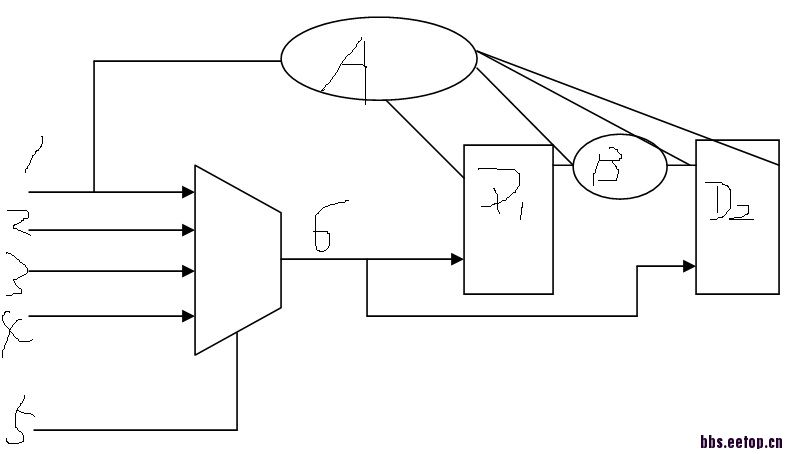

对于这样的一个电路,有四个时钟(1、2、3、4)可以通过选择器添加到线6上。并且时钟1驱动逻辑A,时钟6驱动后面所滑内容。问,在pr时序分析的时候如果通过create_generate_clock或create_clock创建1、2、3、4四个时钟,分析报告就会乱分析,他会分析时钟1和时钟2之间的延迟,但是由时钟线6同一时刻只能有一个时钟频率,请问怎么样使时钟线6上的时钟唯一化,避免由于创建了时钟1、2、3、4而导致pr去分析1、2之间的延迟。用false_path实现不了,因为如果两两false_path就会导致A、B区域的时序被忽略。

对于这样的一个电路,有四个时钟(1、2、3、4)可以通过选择器添加到线6上。并且时钟1驱动逻辑A,时钟6驱动后面所滑内容。问,在pr时序分析的时候如果通过create_generate_clock或create_clock创建1、2、3、4四个时钟,分析报告就会乱分析,他会分析时钟1和时钟2之间的延迟,但是由时钟线6同一时刻只能有一个时钟频率,请问怎么样使时钟线6上的时钟唯一化,避免由于创建了时钟1、2、3、4而导致pr去分析1、2之间的延迟。用false_path实现不了,因为如果两两false_path就会导致A、B区域的时序被忽略。另外,create_generated_clock的-combnitional是怎么用的?

可以用set_clock_group -name XX_mux-locgically_exclusive -group clka -grouop clkb -group clkc -group clkd

试试。

这样4个时钟就单独分析,不会交叉。

这是PT中的命令,PR工具不知道有没有。

1,2,3,4的时钟频率是多少

请问时钟1,2,3,4是异步时钟么?

A逻辑的输出有多个,分别作用在D1,D2的输入端么?

可以设set case analysis,按最快的时钟选择MUX的导通路径。

频率不重要,我就是不想让他出现乱检查的情况

1,2,3,4是同步的我这样画A和B是想表明AB之间有数据传输

这样不好吧,那它就检查不了A被1驱动而B被2驱动的情况了

B为什么会单独受2驱动?B不是应该受1,和选择导通的时钟共同控制的嘛?

我这么问有我的理由

liuada001说的方法基本正确,为什么“它就检查不了A被1驱动而B被2驱动的情况”?

因为1,2,3,4是同步时钟,如果2,3,4是由1分频过来的,那么通过case命令只选择时钟1穿过mux,那工具就只能分析逻辑A被时钟1驱动,而逻辑B也被时钟驱动的情况了,

这样他就分析不了逻辑A被时钟1驱动,而逻辑B被时钟2驱动的情况了

除非搞多个SDC 文件进行分case分析

通过case命选择的是穿过mux的时钟,可以是1,2,3,4里面任意你想要的时钟,当然可以分析逻辑A被时钟1驱动,而逻辑B被时钟2驱动的情况