encounter中tming loop怎样处理?

时间:10-02

整理:3721RD

点击:

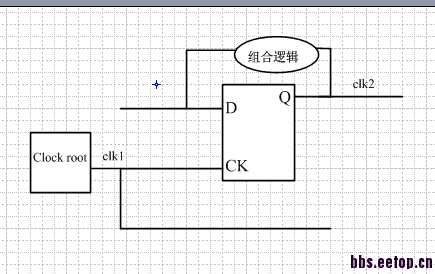

如图中所示:

clk2是clk1的generatedclock, FF的Q通过组合逻辑接回自身的D端,形成一个timing loop,

encounter cts spec中, 是先定义clk1, FF的CK为through pin,

这样的时候, CTS完了之后, optsetup and hold之后, 发现FFQ--->D这里会有hold violation, 如果手动fix hold violation 的话,会在这里造成新的setup violation,

所以想请教各位如何处理这类timing loop?

是要set timing disable么?如果是的话, 具体怎样设置?

通常情况下,这里不构成timing loop吧 ?

請問二樓為何這不是 timing loop?圖畫出來明明就是timing loop~