求问版主以及各位大神关于两路时钟选通的处理方法

时间:10-02

整理:3721RD

点击:

求问各位一个时钟树选通的问题,如何设计以及如何综合约束。

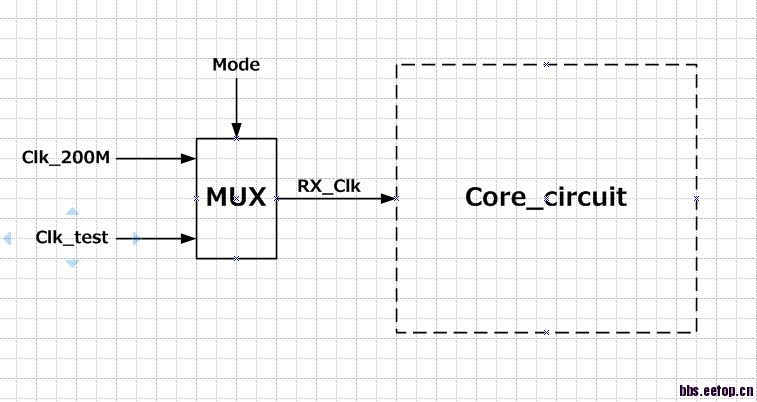

因为本次设计有两个模块,一个是模拟部分,一个是数字部分(下图中只画出了数字部分,表示为Core_circuit)。由于考虑到数字时钟信号可能对模拟电路干扰很大,所以设计中的工作时钟Clk_200M是由模拟电路做出来,然后给到数字电路部分。

由于考虑到可能自己设计出的芯片时钟可能做得不好,导致比如扇出不够,或者时序不满足等问题,所以在测试的时候希望通过另外一个时钟Clk_test来测试数字电路本身的功能是否正确,而非测试的模式下,还是使用自己做的时钟树工作。因此,这里就涉及到对两个时钟Clk_200M和Clk_test进行选通。目前只想到利用MUX对两路输入时钟进行选通,然后得到RX_Clk,输到设计的芯片中(Core_circuit),如下图所示。这里假设Clk_200M是自己做的时钟树,Clk_test是来自FPGA产生的时钟,工作频率比200M低很多,估计低一个数量级。

但是由于时钟经过了一个门电路,势必会造成时序上的不稳定,比如在不同的PVT下,我无法保证设计中约束的时钟与实际的时钟接近,而可能导致芯片最终流片失败。

所以想请问一下各位,对于这种时钟的选通问题,一般是不是就是通过一个MUX来处理?如果利用MUX处理,那么在综合以及后端设计的时候应该如何去约束时序呢?(这里小弟想的是,在综合的过程中,从RX_Clk开始还是认定为理想时钟,设计transition等参数,但是对于MUX这部分应当如何约束比较好呢?然后在后端又应当如何处理呢)一切的一切都源自为了提高设计的可靠性。

或者说可以不考虑这样的设计方案,求各位大神指教。

使用時鐘專用MUX,平衡2路時鐘在MUX上的延遲差

哦,谢谢。今天找了下书,看到了专用CKMUX的做法。我再看看能弄否,谢谢。