锁相环的困惑?

时间:10-02

整理:3721RD

点击:

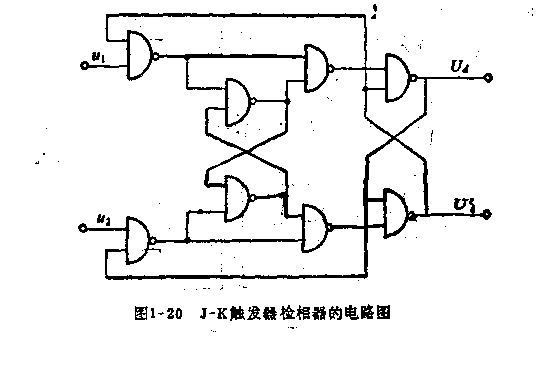

困惑 1: 锁相环的鉴相器有异或们的还有触发器型的请问他们有何不一样! 并请那位大侠给出个触发器型的东东看看? 看过很多例子但大都是异或门的。

困惑 2: 如过我要输入的反馈比较时钟和基准时钟都不是1:1的,请问我要用什么办法来做这个东东?

困惑3:那个XILINX的那款器件允许锁相环的基准时钟为64K?

困惑 2: 如过我要输入的反馈比较时钟和基准时钟都不是1:1的,请问我要用什么办法来做这个东东?

困惑3:那个XILINX的那款器件允许锁相环的基准时钟为64K?

锁相环的困惑?

1.异或门鉴相器鉴相结果和占空比有关,如果PLL做的不好,输入输出虽然同频,且上升或下降沿同相,系统锁定与否和高电平持续时间(占空比)有关。

触发器型鉴相器鉴的实际是边沿,只有上升或下降沿同相,系统即锁定。典型的如教科书上的JK触发器鉴相器等。

2.采用边沿鉴相器鉴相较好。

3.我好象没有找到,只看到Altera 的APEX20系列PLL输入输出最低可以是1.5M。

锁相环的困惑?

re困惑3:Xilinx到目前为止,Xilinx没有一款器件的DLL输入时钟可以达到64K。

锁相环的困惑?

1,除Nicholas 所说外,异或门鉴相器没有鉴频功能,但有的触发器型可以(双D触发器型)。之所以都用异或门型的是易懂。

2,必须用触发器鉴相器。

同问问题2

好牛啊,我一个都不懂 5555555555555555555555555555555

牛人就是牛

学习一下,呵呵

牛人躲在上面说几句,让我们好好学学阿!