计数器的同步级联!

时间:10-02

整理:3721RD

点击:

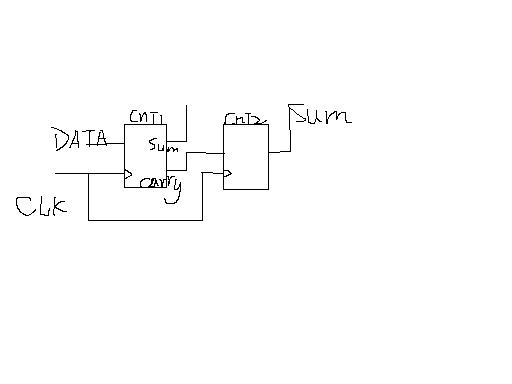

两个计数器,后一个对前一个的进位计数,但是要求两个都是同步计数器,代码应该怎么写呢?最好用verilog:)

[求助]计数器的同步级联!

carry做计数的使能

[求助]计数器的同步级联!

如果是carry做使能端的话,如果存在硬件延时的话,

if(sum==2'b11)

sum<=2'b00;

carry<=1;

else

sum<=sun+1;

carry<=0;

如果考虑硬件延时的话,carry的上升延会在clock后到达第二个计数器,是不是会导致carry的计数要慢了一个clock周期?

如果是2'b11时进位,我觉得可以在10->11时使carry为1,但是如果不是11进位,那么代码就要麻烦多了。比如10进位,要在01时给carry<=1,然后在10时又要使sum跳变回00。

不知道我这样想对不对?:)用不用这样考虑?

[求助]计数器的同步级联!

assign carry = (sum==2'b11)

cnt2

always@(posedge clk)

if(carry)

cnt <= cnt + 1;

else

cnt <= cnt;

[求助]计数器的同步级联!

谢谢小编!:)明白了!:)受益匪浅!:)