Re: 关于单端输出OTA增益与输出电平的关系

另外,如果功耗不苛刻的情况下,不建议使用current mirror OTA,用folded cascode

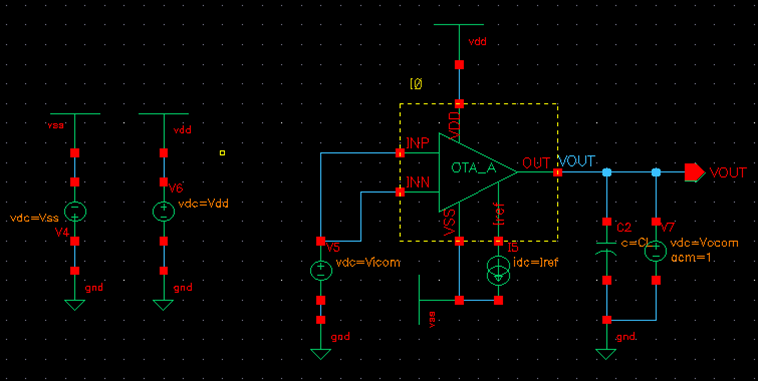

查过DC工作点了,没问题。但是我用dc仿真得出的gm和gds简单计算了一下增益Av,跟仿真不吻合。

当Vout=-0.5V时,仿真Av为87dB,计算得出Av=77dB;

当Vout=1V时,仿真Av为71dB,计算得出Av=74dB;

从计算结果来看,增益下降并不多,但实际仿真发现增益下降了很多。从仿真结果来看,输入管的跨导gm几乎没有变化,输出级NMOS端的rout是增大的,PMOS端的rout是减小的,但减小得并不多。

增益计算公式为:Av=gm*(rout_n//rout_p),rout=(gm2/gds2)/gds2;

为什么folded cascode好于current mirror OTA?是因为噪声吗?

降低Vbn会减小NMOS端的输出阻抗,增益会下降一些。对于提高高输出电平时的增益没用,这个我对Vbn进行过扫描仿真。

这个也试过了,确实可以提高增益,但是改善有限。尤其是在0~1V范围内增益下降严重的趋势还是没有任何变化。

如果想输出swing大,首先别用cascode(这会牺牲增益但得到的曲线较平),如果想增

益较大又swing较大那就用两级甚至三级结构

恩,要增益大而且swing也大,确实得用两级放大结构。这个我也对比过,密勒补偿两级放大器得到的结果确实要好很多。我只是觉得这个现象比较奇怪,想不通是什么原因造成的。不知道是否跟特定工艺PMOS管的特性有关。

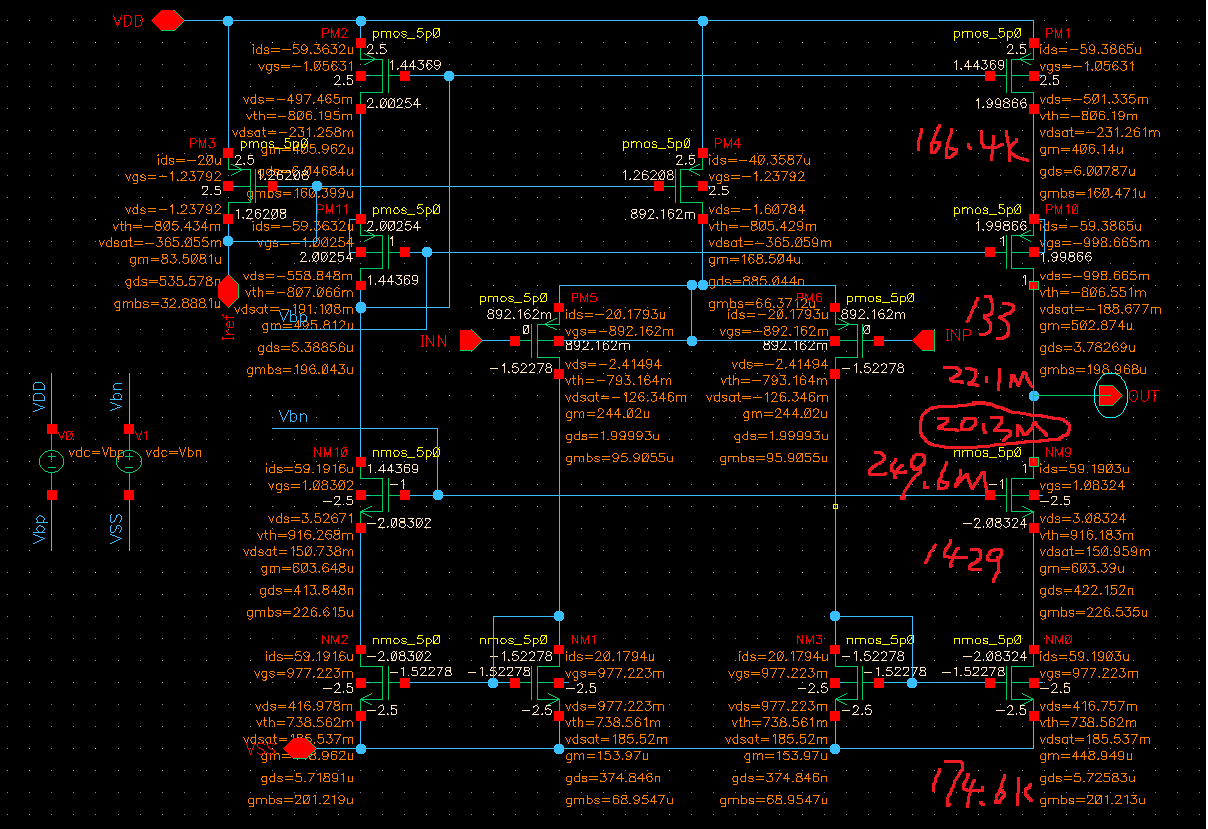

就是因为你cascode管中某一个管子进线性区了所以输出阻抗下降了呀

我用的是正负2.5V供电,输出在0~1V时 PMOS cascode还处于饱和区,没有进入线性区。按理说输出阻抗不应该下降很多的。正是因为这个原因我才感觉很奇怪,无法解释。

工作点肯定是没有问题,这个我确认过。

不过后来我单独仿了一下NMOS管和PMOS管的本征增益随Vds的变化曲线,PMOS跟NMOS差别挺大的,这个应该是跟具体的工艺有关。

这个应该是引起增益在输出高电平时下降比较快的直接原因。

把你在-1V和1V情况下的工作点标一下

vds, vdsat, gds, gm有什么区别

你这图中L变大了显然vth变大得很明显,你确认管子是在饱和区而不是亚阈值区?

让你标注一下dc point你又不信

显示这么多位,你看的不累么。。。

aelPushSignifDigits(6)

恩,看过了,NMOS和PMOS的本征增益与Vds的关系差别挺大的,这个应该是主要原因。

只是DC仿真得出的增益与AC仿真得出的增益差别挺大,不知道哪个更可靠。

dc ac得到的结果应该一样,你看看dcac仿真过程中工作点完全一样吗?

你根据gmro~vds调整下vbn,vbp,使管子处于合适的vds

这里我用DC得到的增益指的是在AC仿真的时候利用DC工作点得出的gm和gds来粗略计算输出阻抗rout,然后乘以输入管的gm得到增益。这个工作点就是AC仿真的工作点,但是两者计算出来差别很大。我知道粗略估算肯定有误差,但是相差太大了。所以想不明白。

vbn和vbp我扫描过了,对增益是有影响,但是增益在高输出电平时快速下降的趋势还是没有变化。

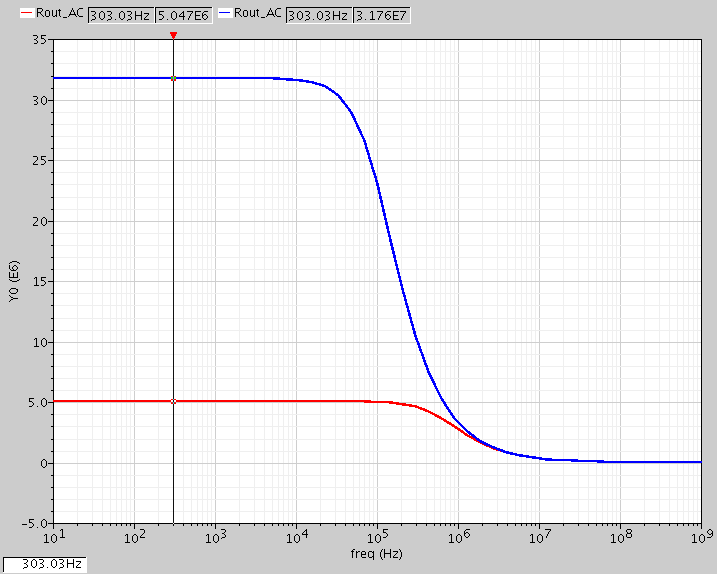

我按照你的说法查看了一下静态工作点。采用AC开环仿真计算输出阻抗,输入静态工作点保持0V不变。分别对比了Vout=-0.5V和Vout=1V两种情况下的静态工作点。发现用直流工作点参数估算的增益与AC仿真得出的低频输出阻抗在Vout=-0.5V时比较接近,分别为29.6Mohm和31.8Mohm. 但是两者在Vout=1V时差别很大,分别为20.3Mohm和5Mohm。

这个现象不知道是什么原因造成的。我觉得用开环AC仿输出阻抗应该没什么问题。

谢谢!

PS:输出阻抗估算公式采用gm/gds1/gds2的形式来估算的。