什么原因会导致ADC输出的高次谐波比低次谐波的功率还高?

我提供的信息不够?pipeline, 10bit, 4+4+4...没有opamp sharing

输入由agilent 33250提供,1M输出的SFDR>75db,refrence外部电源给电压,手册

上的纹波是1~3mv

静态测试DNL<1lsb,INL 2lsb

一个10bit ad,sfdr>75db了为啥还要纠结 有什么意义呢?

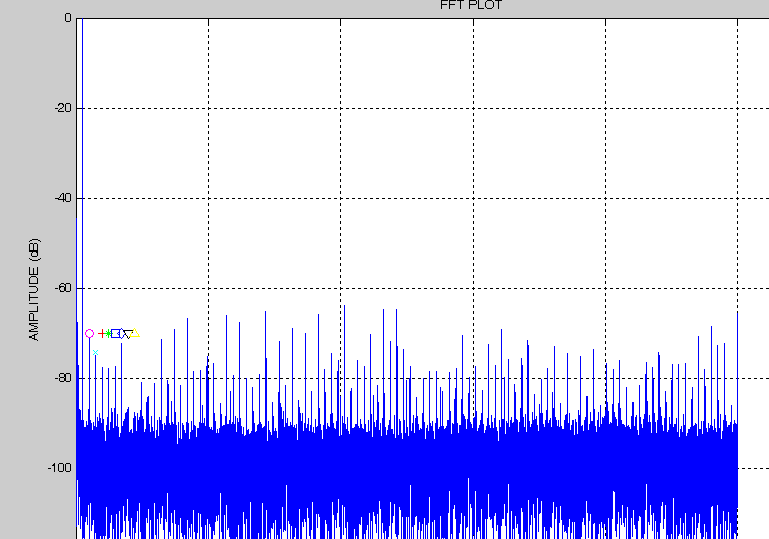

75db指的是1MHz输入信号的....实际上fft出来的结果低阶的谐波其实也-70左右,反而是

高阶的谐波一直延伸到Nyquist,功率较大的在-60左右,贡献了不少distortion...

reference在片外放了10uF,1uF的电容,之前测试用过10nF的电容...

我的理解reference上即使有噪声最后贡献的也不应该是高次谐波啊

有可能是电感的谐振,bonding wire,decoupling电容。

这个电容并不是多了就好,

多了setting就慢了

贴个结果

INL太大造成的吧

感觉cap mismatch不太好,可能会导致高次谐波

如果是OPA或者开关做的不好,一般都是3次高

感觉而已

贴的这个INL是不大好,不过形状差不多,cap mismatch确实有些问题,layout的时候懒了点。

我翻了不少paper,少有这方面的论述,唯一一个提到高次谐波的,是关于memory effect的

看DNL还行啊,INL多比特的话应该变好吧,平均了啊

有没有加点电压试试

板上的解耦电容和芯片近么

有没有测试芯片电源电压稳定么?

电源电压和reference电压的改变会改变ENOB,但这个乱七八糟的高次谐波没有太大变化。总会在很高的奇数次谐波的地方出现最大值。

板子上的decouple应该问题不大,电源电压那示波器看不出来是否稳定啊。看agilent的datasheet电源应该还可以的。

时钟4438C给0dbm的信号,经filter+balun之后进去的

第一级4bits,对电容的mismatch要求不高吧。用的多大的电容?

不过话说回来,你这个INL确实太差了,第一级的问题很大。

有没有给cap做一些特别处理,比如循环翻转什么的...

觉得INL这么大挺奇怪的,怎样的layout才能搞成这么强啊

没有common-centroid...这个INL贴的图有点问题的...应该在+-2lsb

没有Common-Centroid也不至于吧。

你后仿的时候有抽过CC吗?

都抽过...我就是看了某篇paper没用我才没用的....

按照foundry手册上的数据,我的cap值选择应该能保证DNL<0.2LSB...

楼主还是在多个频率下试试,本身这种东西很复杂,需要详细的测试,找切入点,频率变

高,谐波有何变化,幅度变大,有何变化。cap的mismatch不一定是cap本身造成的,连线

也很重要。另外比较器是否有出错的可能,如果比较器的出错呈现一定的信号特性,岂不

是有谐波了?

你的ADC问题解决了么,或许是reference有问题

reference的电压随着电源有波动。也会出现这种情况

呵呵,这么久了还回帖,赞啊

这是我现在最怀疑的地方,可惜,暂时没有空接着测,等测好了回来汇报结果。