两个数字设计的问题

时间:12-12

整理:3721RD

点击:

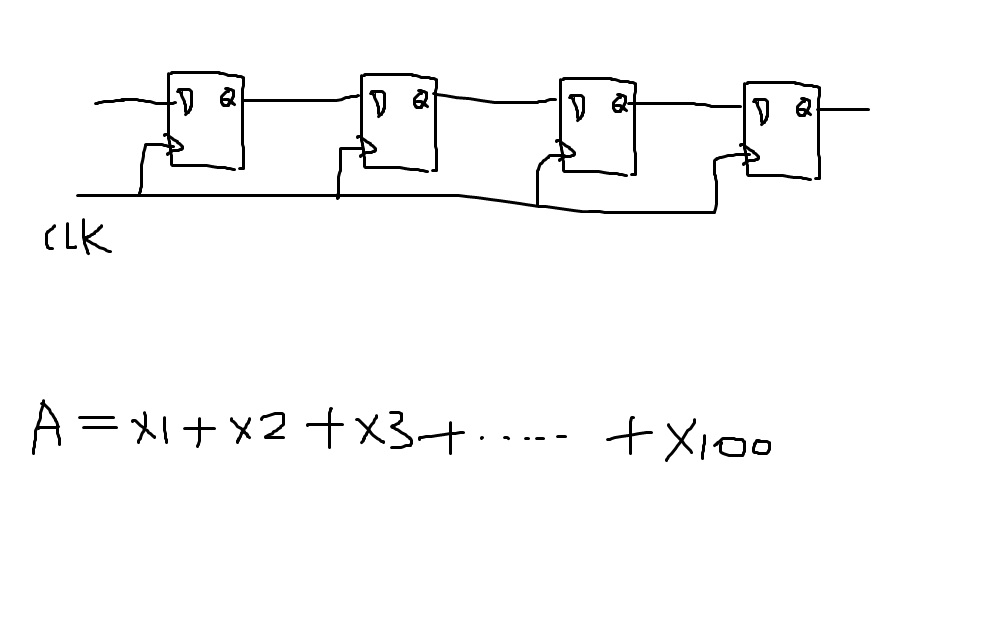

1. verilog代码写了一个寄存器链,如图上部所示。我的目的是实现数据随着时钟节拍向右传递。vcs仿真正确,但是不知道DC综合后得到的网单会不会因为D-Q之间直连造成无法保证hold time的要求?

2. verilog写的许多信号连加起来赋给另一个信号。声明时,A和X系列信号的宽度不一样。请问现在的Design Compiler是否足够智能保证:功能正确,且生成金字塔形状的加法树而不是((X1+X2)+X3)+X4+....

3. 现在写always@(*) Design Compile可以正确处理吗?

谢谢!

2. verilog写的许多信号连加起来赋给另一个信号。声明时,A和X系列信号的宽度不一样。请问现在的Design Compiler是否足够智能保证:功能正确,且生成金字塔形状的加法树而不是((X1+X2)+X3)+X4+....

3. 现在写always@(*) Design Compile可以正确处理吗?

谢谢!

1. Hold Time有BE去保证,一般FE DC synthesis不用考虑hold time

2. 应该没问题,DC会去扩展位数比较少的输入

3. 可以,不过不建议,lint时会报错吧?

1,一般应该是上一个DFF的clk到Q的延时可以保证下一个DFF的holding time吧

你这些问题是太小看S公司了。

我觉得这就是为什么S比C和两个M活的好的原因。

现在不少库的FF的hold time都是负的,就算是正的,做后端时插点buffer也能修掉hold

2,3都不是问题