请教一道题

这个就是没有电平移位的push-pull输出级,如果没有body effect,且P,NMOS亚阈值参数相同,那么输入和输出的电压差近似为0。

我感觉你说的不对,能否详细解释一下,至少你说的和答案有区别

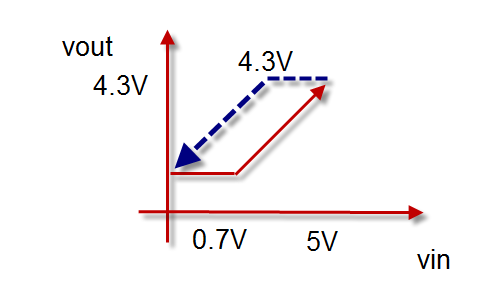

这是答案,我的问题是为什么中间会钳制在2.5V,而不是输入输出一直follow的关系,

刚才有个哥们说的高低电平的输出是对的,不知道为啥删贴了

那输入是0,输出也是0也可以稳定的啊,我觉得输入输出的关系要看输出接点的初始电压时多少。。。

但是仿真和答案类似,输入是0,输出不是0,接近阈值吧。

这个叫crossover distortion. 你这个是Shepard的题么?我们前年在哥大考过。。。

能否详细解释一下,俺不是哥大的

不过哥达的模拟让俺很是敬佩

output=input-0.7 (input>0.7)

input < 0.7, PMOS对output端有负载作用,比如input是0.3V时,output接入的电压大于1V,PMOS就导通了,会拉掉output端电流,此时上面的NMOS一直处于关断状态.

如果没有其他电路,那么input输入小于0.7V,output可以看做是高阻(其实是有条件的高阻状态).

说实话,没看明白 @_@。。。

感觉你说反了吧,下面的PMOS导通时,output=input+0.7,上面NMOS导通时,

output=input-0.7,假设上下两管电阻相等,中间应该迁至在Vdd/2即2.5V,所以从

1.8到3.2之间是平的。可是俺还是不明白为啥到了输出在2.5V就停下来了,不继续

follow了,那时候管子还可以继续导通啊

在0-5V怎么样的输入能使两个管子都导通?

如果不能,那么你的"假设"后面的话就不用看了.

Vin=0v时Vout=0.7v;当Vin逐渐升高时,Vout的电压为什么不是保持0.7v而是线性升高?驱动它升高的电荷来自哪里?

我觉得没有情况两管子都导通,在中间阶段,也就是crossover,应该两个都截至吧

我觉得Vout线性增加是follower的结果,只需保持管子导通即可,如果保持0.7的话,

pmos电流增大,可是没有电流路径,如何增大?

我看了,但是还是不明白为什么不能一直pmos驱动或nmos驱动,需要在中间转换。

答案错了吧?

可是仿真的结果和答案一致啊,问了我们老板,这题是他出的,ms也糊里糊涂的,没好意

思继续追问。

我觉得答案是对的。输出端有对地的电容,当PMOS和NMOS都断开时,电容悬空,电容上的电压保持不变。

当电压从5V降下来,输出电容电压保持4.3V,上面的NMOS没机会倒通,只有等PMOS倒通,这样走的是答案上面的线。反之,若电压从0V升上去,电容电压保持0.7V,下面的PMOS没机会倒通,只有等NMOS倒通,这样走的是答案下面的线。输出点的电容相当于存储了上次的状态。

你看那个wiki上的电路图,上面接VDD,底下接的VSS,而负载接的是GND。

所以当输入在正负0.7之间的时候,两个管子都不导通,输出就是0。当输入较高的时候

NMOS导通,PMOS不通。输入低的时候PMOS通,NMOS不通。

这是输出接电阻的情况,接电容(悬空)好像不一样。

pmos从0v升高时,pmos应该是截止,哪来的导通?

这个跟接电容没啥关系,题目要考察的应该是静态特性吧。

如果悬空的话,负载电阻就是pmos和nmos的本征输出电阻,如果pmos和nmos的输出电阻

是对称的话,就相当于输出接了一个电阻,电阻的另一端接到vdd/2。

题目里的assume是什么意思?和仿真中的model一致吗

仿真结果和答案是差不多的,所以我觉得这个答案是合理的。

照你这么说,你只用一个PMOS管,然后一头接地,栅也接地,你忽然能得到一个0.7V的电压,然后你照这种方法串联多点,你可以发电了.仔细看电路,别自己添加其他条件

我不想和你争,这道题确实不如wiki的图明显且有说服力,但道理都是一样,这点应该能

理解吧。输入0时相当于输入Vss,P管D端也接Vss,这样输出为Vss+0.7,这样解释是合

理的。

木有负载的情况下这个电路木有意义

这个也能争起来.....

是啊,没啥可争的,其实就是领会精神就好了,没必要斤斤计较挑毛剑刺的。上面的一个

哥们给出了wiki上的图,比我的图更有说服力,说明人家是真明白问题在哪