一个的的【微电子中的电容制

时间:12-12

整理:3721RD

点击:

——首先,别笑我这问题问的傻,呵呵。

-

在下述问题中,这个解决方案是否可行——参见最后的问题描述——如果可行的话,怎么这么多年,都没有一个人想到呢?——现在的芯片内部的电容形成方法,还是【打洞】的方法,难道不能借鉴此种思想,用很多【弯曲面】或【凹陷面】来代替直面,以做到增大面积,从而增大可存储的电荷量的作用么?——以此方法增大了电容的容量?——这样可以么?——恰似:活性炭过滤一样,增加好多内部空隙,来增大实际表面积,从而提高过滤效果。

——微电子业界,云集世间一群精英,——却长期没有人这么干过,这说明这佯作肯定是在工程上有问题的,我猜测问题大概有如下几个:

【1】:晶圆上生成电容,常常用打洞的方法,而这样的电容器的两极上打洞,算是在电容上作电容,这可能会使得所做成的电容器的值的精度不好,因为所打的洞的参数或者洞底的边沿处理工艺跟不上(相比于平面,要难处理多),所以可能会洞洞不同,导致做出来的电容精度不好。

【2】:因为表面不平整,所以,在【同性相斥】以及【异性相吸】的共同作用下,导致一个电极板上的电荷空间分布形式会随着其上的电荷总量在不断变化,而分布形式实质上是代表了电荷利用电极板产生所谓的【电容效应】的有效面积,这样就导致了充入的电荷不同,对应于该电荷量,电容的值也不相同——这样的电容就没法使用了。

因为我们通常的电容都是要求值恒定:C=Q/U;这样,我们才好以这个电容值来作为计算的基础。

-

大家还能想出其他的推翻这个方案的工程上的意见么?

亟盼高手相助。

【具体问题】以及对应的【乌托邦式的解决方案】如下所示:

-

【应用背景】: 在DRAM(Dynamic Random Access Memory) 设备中,信息是储存在MOS (Metal-Oxide -Semiconductor)集成电路板的半导体电容器里。

【问题描述】:

目前随着设备尺寸的不断减小,电容器容量受到了限制。需要寻找一种方法,能在缩小电容器尺寸的同时,提高其电容量。

【解决方法】:

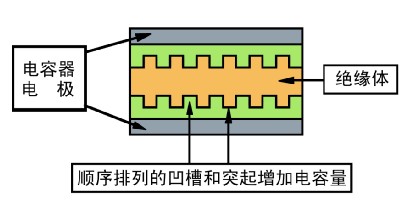

如图可以在电容器的两个电极间上按一定的间隔排列一些比电容器尺寸小的多的凹槽和突起。这样就大大增加了电极的表面积,所以电容量会大大增加,而且不会多占用半导体上的空间。

-

在下述问题中,这个解决方案是否可行——参见最后的问题描述——如果可行的话,怎么这么多年,都没有一个人想到呢?——现在的芯片内部的电容形成方法,还是【打洞】的方法,难道不能借鉴此种思想,用很多【弯曲面】或【凹陷面】来代替直面,以做到增大面积,从而增大可存储的电荷量的作用么?——以此方法增大了电容的容量?——这样可以么?——恰似:活性炭过滤一样,增加好多内部空隙,来增大实际表面积,从而提高过滤效果。

——微电子业界,云集世间一群精英,——却长期没有人这么干过,这说明这佯作肯定是在工程上有问题的,我猜测问题大概有如下几个:

【1】:晶圆上生成电容,常常用打洞的方法,而这样的电容器的两极上打洞,算是在电容上作电容,这可能会使得所做成的电容器的值的精度不好,因为所打的洞的参数或者洞底的边沿处理工艺跟不上(相比于平面,要难处理多),所以可能会洞洞不同,导致做出来的电容精度不好。

【2】:因为表面不平整,所以,在【同性相斥】以及【异性相吸】的共同作用下,导致一个电极板上的电荷空间分布形式会随着其上的电荷总量在不断变化,而分布形式实质上是代表了电荷利用电极板产生所谓的【电容效应】的有效面积,这样就导致了充入的电荷不同,对应于该电荷量,电容的值也不相同——这样的电容就没法使用了。

因为我们通常的电容都是要求值恒定:C=Q/U;这样,我们才好以这个电容值来作为计算的基础。

-

大家还能想出其他的推翻这个方案的工程上的意见么?

亟盼高手相助。

【具体问题】以及对应的【乌托邦式的解决方案】如下所示:

-

【应用背景】: 在DRAM(Dynamic Random Access Memory) 设备中,信息是储存在MOS (Metal-Oxide -Semiconductor)集成电路板的半导体电容器里。

【问题描述】:

目前随着设备尺寸的不断减小,电容器容量受到了限制。需要寻找一种方法,能在缩小电容器尺寸的同时,提高其电容量。

【解决方法】:

如图可以在电容器的两个电极间上按一定的间隔排列一些比电容器尺寸小的多的凹槽和突起。这样就大大增加了电极的表面积,所以电容量会大大增加,而且不会多占用半导体上的空间。

你画的是上下结构还是左右结构?

电容值正比于面积,反比于电极距离。

你这样凹处电极距离较大,电容值反而较小。

中间绿色的是啥?

现在集成电路里有叉指的结构,比你给的这个图还复杂,就电容密度上而言现在的

集成电容器已经非常的大了,但是电路中经常使用PF量级的电容才使得电容的面积看上去很大

你这个结构你算一下,电容值会变小,而且现在的mim做的较大了,你这是天真的想法

DRAM里面之前有过一些解决方案:

1)在衬底挖个坑,以增加正对面积,但是工艺节点往下走对电容的需求增大而工艺上深宽比也做到了很大,所以这个方案也逐渐不被看好了;

2)采用stack capacitor,通过堆叠把电容做大。

最近,已经有新的想法,和lz的类似,具体可以参考veendrick的nanoCMOS的书。

请参照DRAM中的stack 结构,和 tranch 结构。以及所谓的Buried word line结构。

DRAM 里面用2种电容:

1. trench 电容,用挖深槽的方法增加表面积,来提高电容值,

trench cap用的很多,比如IBM / TSMC 的memory里面都是这样的

2。 堆叠电容, stack cap

多年以来, dram的 cap 都是维持在 20~50 ff/um2

随着scaling down , 该值有缩小的趋势, 要尽量大些