高速信号信号完整性问题

时间:10-02

整理:3721RD

点击:

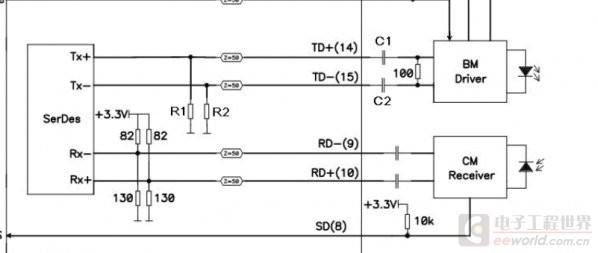

图中右侧是光电转换模块,左侧是处理器差分信号输入输出端。信号速率为10G/s。有如下问题:

1.RD,TD线在serdes端都做了阻抗匹配处理,为何采用两种不同的匹配方式?单向信号是否只在单端做匹配即可?

2.TD,RD线上的耦合电容会不会引起信号反射?

3.PCB走线上的过孔会增加信号的容性阻抗,怎么去定量度量对信号质量的影响?

1.RD,TD线在serdes端都做了阻抗匹配处理,为何采用两种不同的匹配方式?单向信号是否只在单端做匹配即可?

2.TD,RD线上的耦合电容会不会引起信号反射?

3.PCB走线上的过孔会增加信号的容性阻抗,怎么去定量度量对信号质量的影响?

匹配的问题还是建议根据SERDES应用手册设计

至于耦合电容会不会引起信号反射,因为是高速板,确实与PCB布线有点关系,信号传输时遇到的电阻,电容,电感,过孔,PCB转角,接插件,信号都会发生反射

太笼统了啊

因为这个serdes端阻抗匹配不是很熟悉,但这种传输协议方面的,类似我们常用的USB物理特性的匹配一样,都是有协议规定的吧

比如USB的主从设备,在低速和高速的时候,两端的匹配是不一样的,低速的时候在从机的D-线上上拉,高速时在从机的D+上拉,并且还规定了上拉的阻值大小。所以,建议匹配的问题还是建议根据SERDES应用手册设计,熟悉SERDES应用手册设计是必须的

嗯,主要是想问下信号完整性怎样去度量,感觉很多书上只是讲怎么去改善信号质量。实际做pcb设计时候怎么去判断能不能打过孔?走线长度合不合适?噪声是不是足够小?