关于MTK SPI通讯参数含义

时间:10-02

整理:3721RD

点击:

下面是SPI参数源码,我想知道 setuptime holdtime cs_idletime 等变量参数的含义表示什么,有没有设置CLK电平大小的变量

spi->controller_data = (void *)&spi_conf;

chip_config = &spi_conf;

if(!chip_config){

print_log(0, "[ERROR] _SPI config Fail...........\n");

return 0;

}

chip_config->setuptime = 7,//15,cs

chip_config->holdtime = 7,//15, cs

chip_config->high_time = 16,//6 sck

chip_config->low_time = 17,//6 sck

chip_config->cs_idletime = 3,//20,

//.ulthgh_thrsh = 0,

chip_config->cpol = 0,

chip_config->cpha = 0,

chip_config->rx_mlsb = 1,

chip_config->tx_mlsb = 1,

chip_config->tx_endian = 0,

chip_config->rx_endian = 0,

chip_config->com_mod = DMA_TRANSFER,

//.com_mod = FIFO_TRANSFER,

chip_config->pause = 0,

chip_config->finish_intr = 1,

chip_config->deassert = 0,

chip_config->ulthigh = 0,

chip_config->tckdly = 0,

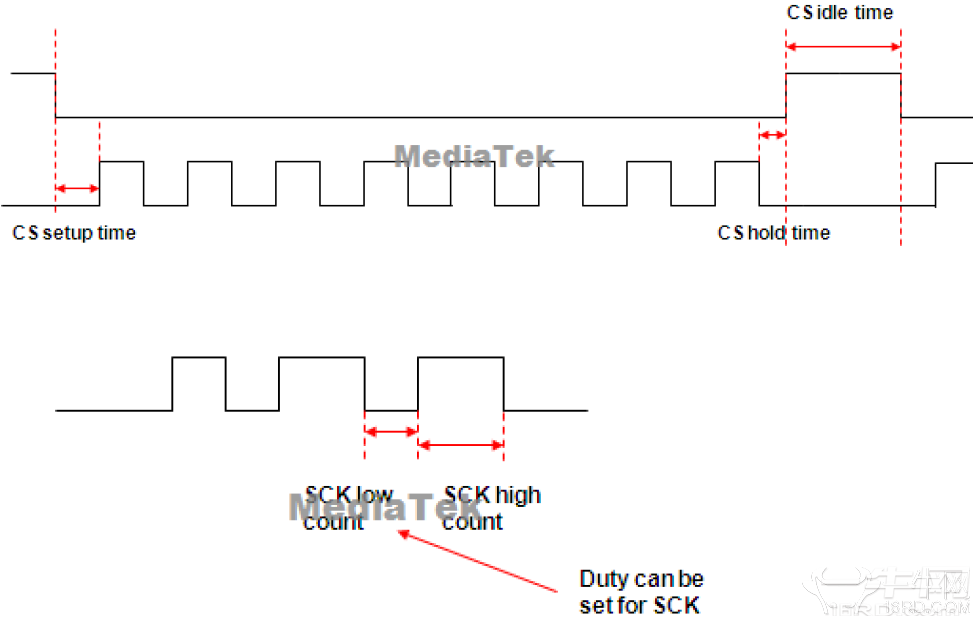

chip_config就是从设备spi_device。对应的时间就是:设定的数值×9.6ns。如low_time = 10*9.6ns =96ns.

chip_config->setuptime = 7,//15,cs cs 建立时间 看上图 7*9.6ns=67.2ns

chip_config->holdtime = 7,//15, cs cs 保持时间 看上图

chip_config->high_time = 16,//6 sck clk 高电平时间 看上图

chip_config->low_time = 17,//6 sck clk 低电平时间 看上图

chip_config->cs_idletime = 3,//20, cs 休眠时间 看上图

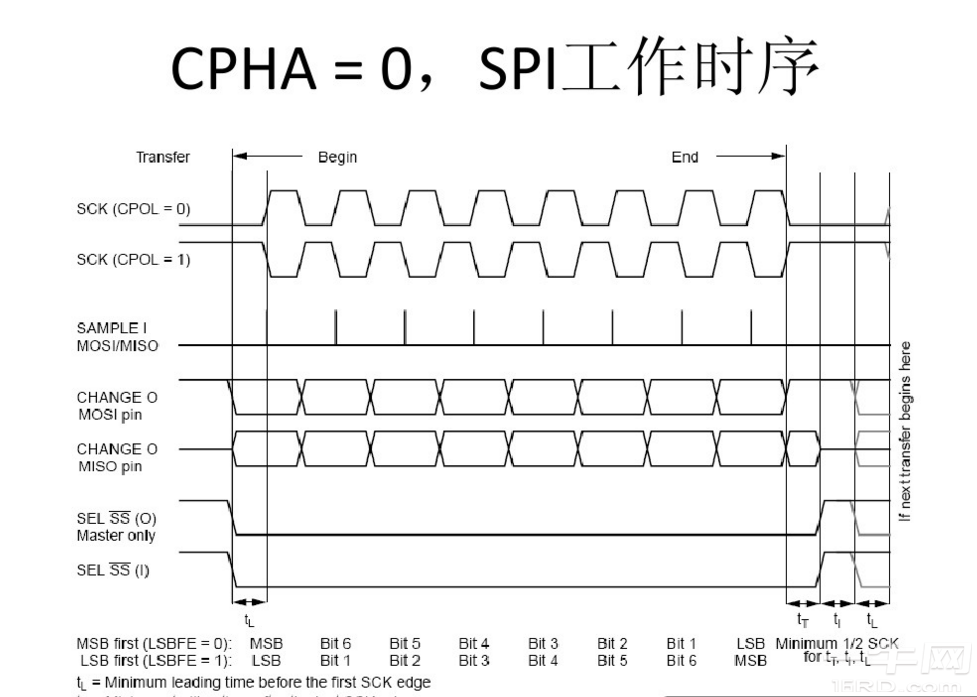

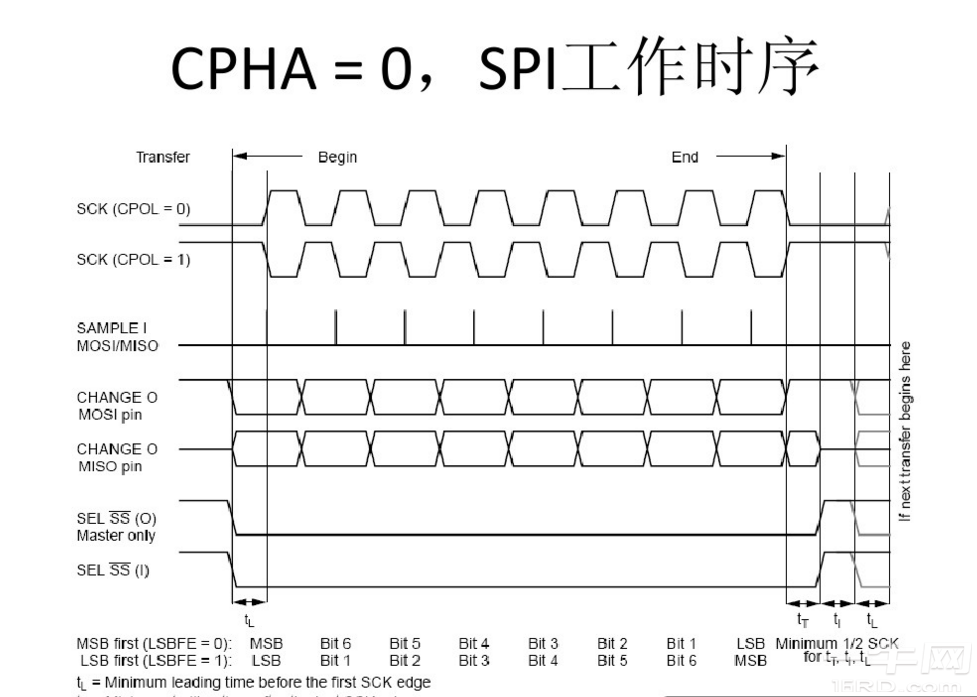

chip_config->cpol = 0, cpol:时钟极性选择,为0时SPI总线空闲为低电平,为1时SPI总线空闲为高电平

chip_config->cpha = 0, cpha: 时钟相位选择,为0时在SCK第一个跳变沿采样,为1时在SCK第二个跳变沿采样

chip_config->rx_mlsb = 1, rx_mlsb & tx_mlsb:传输数据时,先从低bit发送还是高bit发送,1时代表先从低bit发送

chip_config->tx_mlsb = 1,

chip_config->tx_endian = 0, 传输数据时,以大端模式传输或者小端模式传输,只对DMA传输有效,0时,代表小端模式传输; fifo mode为小端模式。

chip_config->rx_endian = 0,

chip_config->com_mod = DMA_TRANSFER, DMA或者fifo 传输

时钟极性和相位看下图

工作方式1:

当CPHA=0、CPOL=0时SPI总线工作在方式1。MISO引脚上的数据在第一个SPSCK沿跳变之前已经上线了,而 为了保证正确传输,MOSI引脚的MSB位必须与SPSCK的第一个边沿同步,在SPI传输过程中,首先将数据上线,然后在同步时钟信号的上升沿 时,SPI的接收方捕捉位信号,在时钟信号的一个周期结束时(下降沿),下一位数据信号上线,再重复上述过程,直到一个字节的8位信号传输结束。

工作方式2:

当CPHA=0、CPOL=1时SPI总线工作在方式2。与前者唯一不同之处只是在同步时钟信号的下降沿时捕捉位信号,上升沿时下一位数据上线。

工作方式3:

当CPHA=1、CPOL=0时SPI总线工作在方式3。MISO引脚和MOSI引脚上的数据的MSB位必须与SPSCK的 第一个边沿同步,在SPI传输过程中,在同步时钟信号周期开始时(上升沿)数据上线,然后在同步时钟信号的下降沿时,SPI的接收方捕捉位信号,在时钟信 号的一个周期结束时(上升沿),下一位数据信号上线,再重复上述过程,直到一个字节的8位信号传输结束。

工作方式4:

当CPHA=1、CPOL=1时SPI总线工作在方式4。与前者唯一不同之处只是在同步时钟信号的上升沿时捕捉位信号,下降沿时下一位数据上线。

spi->controller_data = (void *)&spi_conf;

chip_config = &spi_conf;

if(!chip_config){

print_log(0, "[ERROR] _SPI config Fail...........\n");

return 0;

}

chip_config->setuptime = 7,//15,cs

chip_config->holdtime = 7,//15, cs

chip_config->high_time = 16,//6 sck

chip_config->low_time = 17,//6 sck

chip_config->cs_idletime = 3,//20,

//.ulthgh_thrsh = 0,

chip_config->cpol = 0,

chip_config->cpha = 0,

chip_config->rx_mlsb = 1,

chip_config->tx_mlsb = 1,

chip_config->tx_endian = 0,

chip_config->rx_endian = 0,

chip_config->com_mod = DMA_TRANSFER,

//.com_mod = FIFO_TRANSFER,

chip_config->pause = 0,

chip_config->finish_intr = 1,

chip_config->deassert = 0,

chip_config->ulthigh = 0,

chip_config->tckdly = 0,

我也想知道,坐等回复

D:\23.png

chip_config就是从设备spi_device。对应的时间就是:设定的数值×9.6ns。如low_time = 10*9.6ns =96ns.

chip_config->setuptime = 7,//15,cs cs 建立时间 看上图 7*9.6ns=67.2ns

chip_config->holdtime = 7,//15, cs cs 保持时间 看上图

chip_config->high_time = 16,//6 sck clk 高电平时间 看上图

chip_config->low_time = 17,//6 sck clk 低电平时间 看上图

chip_config->cs_idletime = 3,//20, cs 休眠时间 看上图

chip_config->cpol = 0, cpol:时钟极性选择,为0时SPI总线空闲为低电平,为1时SPI总线空闲为高电平

chip_config->cpha = 0, cpha: 时钟相位选择,为0时在SCK第一个跳变沿采样,为1时在SCK第二个跳变沿采样

chip_config->rx_mlsb = 1, rx_mlsb & tx_mlsb:传输数据时,先从低bit发送还是高bit发送,1时代表先从低bit发送

chip_config->tx_mlsb = 1,

chip_config->tx_endian = 0, 传输数据时,以大端模式传输或者小端模式传输,只对DMA传输有效,0时,代表小端模式传输; fifo mode为小端模式。

chip_config->rx_endian = 0,

chip_config->com_mod = DMA_TRANSFER, DMA或者fifo 传输

时钟极性和相位看下图

工作方式1:

当CPHA=0、CPOL=0时SPI总线工作在方式1。MISO引脚上的数据在第一个SPSCK沿跳变之前已经上线了,而 为了保证正确传输,MOSI引脚的MSB位必须与SPSCK的第一个边沿同步,在SPI传输过程中,首先将数据上线,然后在同步时钟信号的上升沿 时,SPI的接收方捕捉位信号,在时钟信号的一个周期结束时(下降沿),下一位数据信号上线,再重复上述过程,直到一个字节的8位信号传输结束。

工作方式2:

当CPHA=0、CPOL=1时SPI总线工作在方式2。与前者唯一不同之处只是在同步时钟信号的下降沿时捕捉位信号,上升沿时下一位数据上线。

工作方式3:

当CPHA=1、CPOL=0时SPI总线工作在方式3。MISO引脚和MOSI引脚上的数据的MSB位必须与SPSCK的 第一个边沿同步,在SPI传输过程中,在同步时钟信号周期开始时(上升沿)数据上线,然后在同步时钟信号的下降沿时,SPI的接收方捕捉位信号,在时钟信 号的一个周期结束时(上升沿),下一位数据信号上线,再重复上述过程,直到一个字节的8位信号传输结束。

工作方式4:

当CPHA=1、CPOL=1时SPI总线工作在方式4。与前者唯一不同之处只是在同步时钟信号的上升沿时捕捉位信号,下降沿时下一位数据上线。

学习了

学习学习

路过帮顶,顺便学习