参考平面与高速信号换层,10层PCB

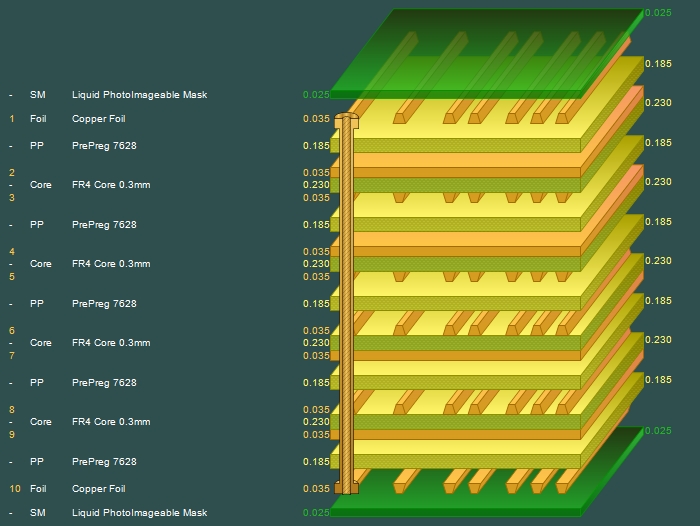

板子叠层如下图所示:

说明:

2/4/7/9平面

1/3/5/6/8/10走线

铜皮:0.035mm (1盎司)

芯板:0.3mm

PP片:7628 (0.185mm)(所有PP片都用7628的)

阻抗:单端50欧姆,差分100欧姆

Top:单端线宽12mil;差分线宽5mil,间距6mil。

Layer2:平面。

Layer3:单端线宽5mil,差分线宽4mil,间距9mil。

Layer4:平面。

Layer5:单端8mil,差分线宽5mil,间距8.5mil。

Layer6:同Layer5。

Layer7:平面。

Layer8:同Layer3。

Layer9:平面。

Bottom:同Top。

设计中包含一片Virtex-4 SX55,FF1148脚的FPGA;一个AD9736,1.2Gsps的DAC;一个AD9518,提供LVPECL时钟;一个AD9957,1Gsps的QDUC。

数据率大概是这样的,FPGA到AD9736是LVDS DDR,时钟450MHz,数据900Msps;AD9957工作在900Msps,数据总线是CMOS的,225MHz;AD9518分别提供900MHz的时钟给AD9736和AD9957。

由于板子面积有限,所以采用多层设计,不可避免的要将高速信号分层,现在的问题是,信号分层必然导致参考平面的不连续,我原来打算在L3/L8层走高速信号,包括LVDS和CMOS,请问,把总线分在L3/L8走,能跑到这么高时钟吗?在这个时钟下,Allegro仿真结果可信度有几分?

问题描述比较长,见谅

应该没问题,总长度控制一下,加匹配电阻。

不过叠层不是很好,建议

1 信号 TOP

2地

3信号

4信号

5地

6电源

7电源

8地

9信号

10信号

911地

12信号 BOTTOM 因为估计你电源是要分割的在4,7层的话万一穿分割平面就不好了

加两层,如果成本不是很敏感的话。此外,加两层地后,你3,4,9,10 都是一样的好的信号层,把不同的DDR的数据线走不同层,就不需要多余的换层了,不是一举多得

感谢楼上的回复,这里的数据基本上都是从FPGA流出,单向的;匹配电阻考虑到了,FPGA带DCI,对于CMOS,可以控制输出阻抗。

由于我的叠层里面,L2是地,L4/L7/L9是电源,平面间不相邻,这样的话高速信号是不是只能在芯片附近换层,回流是不是必须得走芯片的去藕电容,而无法利用平面间的电容了?

ps:这个板子的top曾还有模拟的中频电路,怕干扰。

我们也做FPGA板,基本上10层以上,我有个问题,就是说微带线,上下两层都是平面,一层是完整的,一层是分割的,这样的微带线算不算跨平面

电源层最好和地层相邻近,否则回留环路和 电源耦合会差,独立的电源(相邻层不是地的情况)是万不得以的方法。

高速信号L3走,参考你那个可怜的唯一的地层 呵呵!而表层 你有不能走高速线(EMI考虑),你的高速线的走线层有点紧张的,如果参考电源层的话,回流先经过电源平面,在芯片附近,就要通过连接地和电源的电容回到地上,至于平面间不在芯片管脚附近的电容,是基本利用不上的,回流路径选择阻抗/感抗)最小的路径,如果你的线只有电源平面做参考,那就只能先从电源平面回流,流到芯片管脚附近,最后通过电容到地。

另外,你的电源平面最好不要有分割,分割的话就不能有线跨平面

模拟电路不被干扰的原则就是,在模拟区域不走一条数字线。包括数字电源,也就是你在模拟区域挖空(地不要挖,只挖电源)模拟电源用走线连接都可以的。数字线不要在别的层穿越模拟区,除非有地层分割(电源层分割不行),因为数字电源也是比叫脏的,在模拟区域里有的话,NOISE会耦合上去的。

回5楼的,看和那个距离近,如果你分割的平面距离你的线有20MIL以上,而地和线很近,比如4MIL那问题不是很严重(偏移的带状线),但是一般多层板带状线,上下两层都很近,所以还是应该按照分割平面的问题来考虑,当然比单独的跨分割平面要好多了。如果是单独跨分割,有阻抗不连续和辐射问题,你这样的话,阻抗不连续的问题占主要,辐射问题不大,有地在么。呵呵

楼上的解释的好到位啊。呵呵。看了之后受益不少啊。谢谢啦。

还有给问题请教下哈:

在PADS2007中。放大缩小的功能用不了了怎么办啊。各位有没有遇到过这样的问题啊。我快急死啦。

知道的帮帮偶啊。

呵呵小编这么紧张,你的才几百M不会有问题的allegro完全可以除非到了10Gb以上的信号总线才考虑用ansoft。你那个问题不是很大就是算上3次谐波都没到1Gb。所以allegro完全OK。我们一块2Gb的DDR也是类似叠构的。当然也看具体情况了。

我也正在搞一个类似的系统,CPCI结构,一片Virtex-4 SX35,FF668脚的FPGA;两个AD9736,1.2Gsps的DAC;两个AD9910,1Gsps的DDS,还有一堆模拟的东西。

望讨论。Email:zire72_lee@126.com

刚开始PCB仿真,10曾12曾还在考虑

学习了&

感谢六楼和八楼的朋友,解决了不少困惑,正在考虑增加地平面

地平面太少,太可怜,最后还是增加了一层地平面,这样一来,就有两层地平面,可以走四层高速信号线,合理的叠层应该这样

1-TOP/2-PWR/3-SIGNAL/4-GND/5-SIGNAL/6-SIGNAL/7-GND/8-SIGNAL/9-PWR/10-BOTTOM

如果电源层需三层,可以这样

1-TOP/2-GND/3-SIGNAL/4-PWR/5-PWR/6-SIGNAL/7-GND/8SIGNAL/9-PWR/10-BOTTOM

实际上我选择的后者,三层电源两层地,除去顶层和底层外,还有3/6/8是有地平面参考的完整信号层。目前板子还没出来,出来后把调试结果再贴出来:)

你用的叠层还是不好啊,虽然结果可以过,但是,不是最优的!

学习了!

有个问题问一下ut_pcb:

2地

3信号

4信号

5地

像你说的这个结构中,3、4层的间距要多大,才不会有串扰,这两层信号需要呈垂直交叉吗?

回楼上,要想避免的话至少3倍的线宽,上下间距的话一般3-5倍线宽就可以了,但是平行距离越长,间距要越大。

看你实际的走线了

尽量不要更换参考平面

小编在13楼的叠层2不太好。

4、5两个电源平面在一起而且旁边没有地平面,会造成很大电源噪声耦合。而且电源越过3、6两层分别与2、7两层地耦合,电源上的干扰会直接影响3、6层的信号的。

而第一种叠层中第二层和倒数第二层都是电源平面,不管主芯片放在top还是bot,都没有地平面吸收,也不太好,

小编的板子应该是用于通信设备的,这类板子对成本要求一般不高吧。

至于用10层还是12层,主要看你V4的IO用了多少,好像1148的V4SX55全IO口是640个左右吧,看你使用了多少。

以前我做的一个用了400多个IO,10层板做的,叠层是

top-gnd-s-gnd-s-power-gnd-s-power-bot

(一般这类板子FPGA、AD、DA、CLK chip等均布置在一面如top,底层放一些小器件等,可将BOT铺地看作地平面,power2放倒二层也可有较好的耦合。整板使用最多、电流大的电源走6层)

象这种板子需要几个电源层取决于V4的电源种类。用2个电源层应该够了,V4的电源分得不是很碎,重点是核心电压1.2V,要保证足够的内层通道,可同辅助电压2.5V共一层,位于1.2V通道上2.5V的点用线拉就行。3.3V的IO比较散,要一整层,同时你可能还有别的电压但一般点比较少吧,可以信号层拉线处理。

如果你的IO用得较多,建议12层。层叠:

top-gnd-s-power-gnd-s-s-gnd-power-s-gnd-bot

注意的是6、7两层尽量正交走线,FPGA扇出后尽量分开不要同方向平行走线。

供参考。

以上我所言的叠层方式中带状线与gnd的距离设置得比和power的距离小一些,根据信号以近平面回流的原则,你的所有信号几乎都可以走高速线。

我倒是觉得1比2好多了~~~

2要做到走线层都有GND做参考,那么板子不会对称,会翘曲。当然,你能接受也无所谓。

你好!看你做的是模数混合的电路,你的几个电源层都是数字电源吗,那你的模拟电源和模拟地是怎末安排的?

奇怪!既然是模数混合的电路,为何不见模拟电源和模拟地,难道你的模拟区域不用分割吗,1G的信号频率比较高啦,不怕干扰模拟信号,影响精度吗?

6楼所言极是。

请问12层的层叠可不可以这样:

top-gnd-s-s-gnd-power-power-gnd-s-s-gnd-bot

或

top-gnd-s-gnd-s-power-power-s-gnd-s-gnd-bot

这两的层叠与top-gnd-s-power-gnd-s-s-gnd-power-s-gnd-bot

那个更优化,为什么?