[求助为何发送端的波形如此。

时间:10-02

整理:3721RD

点击:

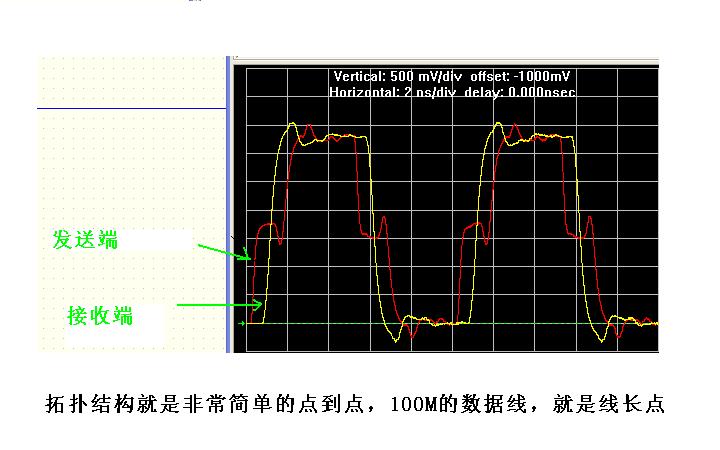

如图为何发送端的波形如此。

做个前端匹配,大概33到50欧姆左右,看看效果如何。

发送端得波形的台阶 :是因为发送端的输出阻抗跟传输线的阻抗分压的结果。

台阶之后的下冲是因为接收端的负载电容过大的原因。

端接匹配没做吧,可以尝试在接收器终端并联一电阻到地,阻值与传输线特征阻抗相近

谢谢楼上的回复,上面这些匹配方式都做了,源端串接电阻小了发端波形没啥改善,反而收端的波形延迟很大,如果发的波形好一点的话串接电阻在330但此时收端的波形已无法容忍。

并联电阻如果取值和阻抗值差不多,发端的波形有改善,但第一个过冲还是很大,并且此时的收发端波形幅度都减小了原来的一半,如果增加并联电阻值幅度满足了但发端的波形就有和前面的一样了。

另外也试过AC、戴维宁的匹配方式都没办法满足改善发端的波形(在保证收端的波形比较好的情况下)。

真不知道到后面的PCB走线如何解决。请问发端如果是这样的波形会不会影响设计的性能和结果。上面这个波形是保证收端的波形前提下试出的比较理想的结果,就是担心发送端的波形会不会影响设计。

仿真时发送端的波形不用去管,只要接收端波形满足要求就可以了!

不信你可以回板后测测看

不用管发送端的波形,你为什么关心发送端的波形呢?没有用的,主要是因为信号的反射造成发送段波形有台阶的。