关于LVDS信号的等长问题

最近在做一个LVDS的电路设计。大体是:芯片接收1路差分信号(最高1.5Gb/s),转成5路并行的LVDS信号加上一个LVDS时钟,连接到FPGA。

1、 LVDS信号需要等长。这个等长,除了同一对LVDS信号的2条线外,这个设计中的5路并行LVDS信号与LVDS时钟是否也需要等长?

2、另外,LVDS需要加端接(所用FPGA内部没有内嵌的端接电阻),可由于板上面积所限(只是修改原来板子的一部分,其他部分不能动,所以限制比较多。),5路端接电阻与FPGA之间的距离不能一样。比如,第1路的线长为:1621+192=1813mil(两端被端接电阻分开),第2路线长为:1504+310=1814mil。两路的线长总的差不多,可由于端接电阻的位置问题,使得整个信号长度被端接电阻分开的两端有所差异。如果并行的LVDS也需要等长,这个等长是指全部线长的等长,还是指端接电阻一边的等长呢?

刚工作2个月,头一次接触,没啥经验。有点头疼。望赐教。

谢谢。

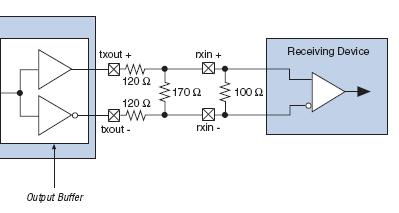

系统中还有2路输出,与上边提到的那个输入的信号是对称的。问题2中提到的端接电阻指的是输出上的。按照FPGA的要求,每路LVDS输出的端接要3个电阻:2个分别串到LVDS的2个信号上,然后1个电阻再并到两线间。2路×(5+1)对/路×3个/对,所以,端接电阻就多了。

1、同一对LVDS信号的2条线肯定是要等长的,设计中的5路并行LVDS信号与LVDS时钟是否要等长需要看你的具体设计包括信号的速度,不过有条件的话一般都布等长。

2、并行的LVDS等长是指全部线长的等长,也就是端接两端总长相等。端接的位置只要靠近接收端就可以了,没有太大的限制。

多谢。:)

很有收获啊

不错,还是有收获的