SOS---关于阻抗测试线互相干扰的问题

紧急求助!谢谢各位大虾!

你在計算第2層阻抗時, 必須同時把1,4層都當做參考平面,

同樣在計算第3層時也是.

用polar試算時請選上下都是參考層,中間是阻抗線的model來計算

1、4是否都接地了

不好意思,应该是第2层阻抗的参考层为第1、4层,第3层阻抗参考层为第1、4层,2、3层的阻抗线之间没有屏蔽层。实测总是比理论计算大约20欧,弄不清楚什么原因。

若是選取的模型無誤, 參考層也確實相接的話,

再來就請板廠做切片, 以實際的數據與模擬的數據做比對.

我的理论计算用的就是板廠切片的数据代入模拟器去计算的,计算出来的值跟原来设计的值差不多,但实测值就是大大约20欧,所以才不明白问题出在哪里。

板材的Er值?

還是你把模擬的數據與切片數據一起po上來, 大家看看.

另, 驗証阻抗的儀器是?

驗証的地方是另外的coupon或是直接驗証板中的線路?

若是另外的coupon, 則確認一下1,4層是否有導通?

若是板中的線路, 那也先要把1,4層暫時先短路起來再做量測.

小弟用過Tek 11801C+SD-24, 小弟的客戶用的是Polar的PCB專用機.

這兩種測試的結果也不盡完全相同.

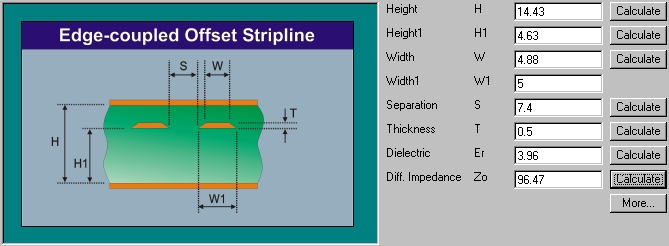

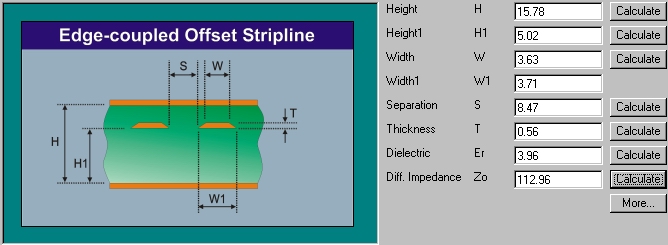

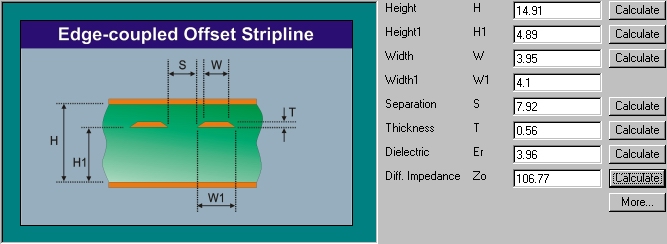

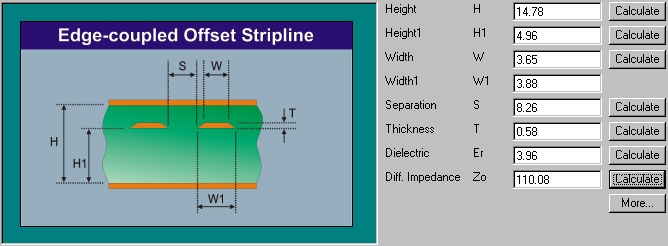

阻抗 | 设计值(mil) | 实测值(mil) | ||||

100欧 | 117.7Ω | 118.86Ω | 116.8Ω | | ||

W | 4.88 | 3.95 | 3.65 | 3.63 | ||

W1 | 5.0 | 4.1 | 3.88 | 3.71 | ||

S | 7.4 | 7.92 | 8.26 | 8.47 | ||

T | 0.5 | 0.56 | 0.58 | 0.56 | ||

H | 14.43 | 14.91 | 14.78 | 15.78 | ||

H1 | 4.63 | 4.89 | 4.96 | 5.02 | ||

設定100

設定100 實測116.8

實測116.8 實測117.7

實測117.7 實測 118.86

實測 118.86

小弟套了一下您的數據, 結果如上比較奇怪的地方是, 您的切片116.8這組數據

線最細, 線距最遠, 阻抗卻最低, 不太合理.

不知您在量測上可否再確認?