powerpcb 问题收集答疑

我先说一个,内层分割的问题,我一直没用过这个功能,4层板,中间层铺铜的时候也可以铺几个不同的网络,刚看了以前的一个贴子,说是不能这样铺,我还是不理解内层分割和直接铺铜的区别。

在说一个,差分线的问题,网上说了好多,还是不知道怎么做出来它,你说具体点好不?

人呢?

小编真是个热心的人,好人一生平安!

我想请教LZ一个问题:

pads里面做BGA的封装时,对pin的定义有数字命名比如1.2....脚.也有用字母与数字一起命名比如A1.A2...

元件做好了后存盘,此时pin脚上两种名字都有,但再打开或者再编辑时候发现只有数字命名的了。字母与数字的就没有了

当然。再import alphanumerics...一次这个字母与数字命名的pin又有了

但是这样的话有一个问题,就是: 如果原理图里面的IC是用字母数字来定义pin的,那么它就在PCB里面找不到对应的元件.

谢谢!

以下是引用xfcy在2008-1-22 11:21:00的发言:

我先说一个,内层分割的问题,我一直没用过这个功能,4层板,中间层铺铜的时候也可以铺几个不同的网络,刚看了以前的一个贴子,说是不能这样铺,我还是不理解内层分割和直接铺铜的区别。

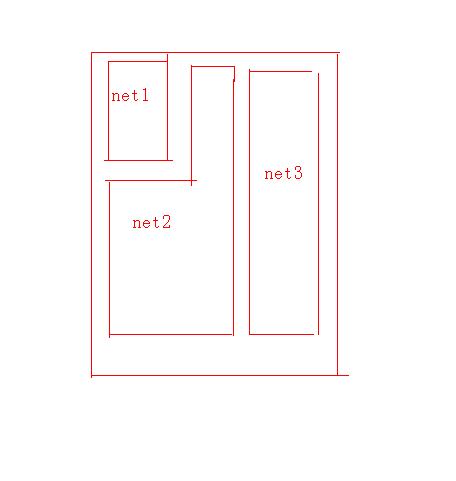

呵呵,好久没有做过内层分割的板子了,不知道是不是说的下面两种情况

内层分割

这种直接用 pour manager的flood就可以铺铜了

直接铺铜

两者都可以铺铜的,的二种比较麻烦一些,先用flood,net2会铺上,net1和net3不会铺,就需要选中shap,右键 flood来铺铜,但是一执行pour manager 里面的flood ,net1和net3就会没有铺铜,从新执行前面的动作

以下是引用xfcy在2008-1-22 11:27:00的发言:

在说一个,差分线的问题,网上说了好多,还是不知道怎么做出来它,你说具体点好不?

你指是指怎样把两个网络定义成查分线,然后在布线的时候两个网络一起走线,是吗?

以下是引用merry在2008-1-23 10:18:00的发言:

我想请教LZ一个问题:

pads里面做BGA的封装时,对pin的定义有数字命名比如1.2....脚.也有用字母与数字一起命名比如A1.A2...

元件做好了后存盘,此时pin脚上两种名字都有,但再打开或者再编辑时候发现只有数字命名的了。字母与数字的就没有了

当然。再import alphanumerics...一次这个字母与数字命名的pin又有了

但是这样的话有一个问题,就是: 如果原理图里面的IC是用字母数字来定义pin的,那么它就在PCB里面找不到对应的元件.

谢谢!

bga器件确实存在这种情况 建好的库 再打开或者再编辑时候发现只有数字命名的了。字母与数字的就没有了

但是如果原理图里面封装指定对,pcb库里面的part type和原理图又一样的话,导入bga器件是可以的

你所说的“如果原理图里面的IC是用字母数字来定义pin的,那么它就在PCB里面找不到对应的元件”.

我遇到的情况最多的是二极管和三极管,这类器件,到目前为止,我没有很好的办法,只能把这些器件的pin mumber改成纯数字的,我不知道你是怎么解决的,也希望有知道的高手指教

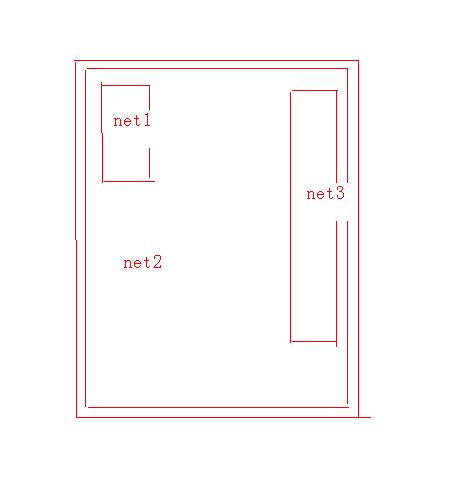

1.内层分割,小编画 的第2个图可以定义铺铜的优先级,net1 net3没有交叉可定义为同一级别,net2要低一级别,行pour manager 里面的flood ,3个网络全部OK,我是想问这样做和内层分割有什么不同。

2.有的网络要差分走线,比如说USB的 D+,D-,我是想问怎么实现差分走线。

以下是引用xfcy在2008-1-23 12:56:00的发言:

1.内层分割,小编画 的第2个图可以定义铺铜的优先级,net1 net3没有交叉可定义为同一级别,net2要低一级别,行pour manager 里面的flood ,3个网络全部OK,我是想问这样做和内层分割有什么不同。

2.有的网络要差分走线,比如说USB的 D+,D-,我是想问怎么实现差分走线。

差分线的定义和走线,网上有很多资料啊,而且都比较详细,按照步骤做就可以了,多练习几次,详细的操作恐怕很难说清楚,看我有空了,发个视频上来

我尝试了很多次,都不能成功.并且我也确定元件的封装都指定对了.只是因为PCB封装做好后pin脚存不到字母加数字的,而原理图里的IC Pin脚又是字母加数字的。所以import到PCB去的时候都会提示找不到这个元件。现在也很无奈的只能在原理图里把这些IC的Pin改为数字的.

但我觉得不可能这个是唯一的解决办法.太耗时间了。几百个pin啊!

而且很奇怪的一点:我以前用PADS2005,和PowerPCB4.0的时候,也做过BGA的元件,当然,原理图里此IC的pin定义都是用的字母加数字的,但都可以成功import.为什么现在就不行了呢?

难道软件版本升级会出现这样的问题?

小编好人哪。

以下是引用merry在2008-1-23 13:39:00的发言:

我尝试了很多次,都不能成功.并且我也确定元件的封装都指定对了.只是因为PCB封装做好后pin脚存不到字母加数字的,而原理图里的IC Pin脚又是字母加数字的。所以import到PCB去的时候都会提示找不到这个元件。现在也很无奈的只能在原理图里把这些IC的Pin改为数字的.

但我觉得不可能这个是唯一的解决办法.太耗时间了。几百个pin啊!

而且很奇怪的一点:我以前用PADS2005,和PowerPCB4.0的时候,也做过BGA的元件,当然,原理图里此IC的pin定义都是用的字母加数字的,但都可以成功import.为什么现在就不行了呢?

难道软件版本升级会出现这样的问题?能不能把导入网表后弹出那个文件(ECO.ERR)的内容拷贝上来看看,注意,pcb库里面改器件的part type必须和原理图里面该器件的一致哦

那个eco.err的内容是说:每一个信号的连接必须要有不少于两个的网络.所以只有一个讯号的网络全部删除掉了.______当然,删除的全部都是BGA IC连接出来的信号,因为这个IC在PCB库里找不到。

因为我一直改元件,后面把IC PIN改为数字的就OK了。所以,那个错误的文件我也就没有了。但意思就是我上面说的,可以肯定是IC PIN脚定义的问题.

再请教LZ一个问题.关于两个文件同步的:

比如现在我手头有一个原理图文件,DRC, Create Netlist都OK.我还有一个PCB文件,此PCB文件里的元件,布线什么的基本上跟我此原理图很相似,但他们的命名不一样,以及网络名也有些不一样,比如在原理图里叫U1,在PCB里面是叫7300.当然元件,封装以及接线都是对应的,也就是说哪个元件出来该接什么讯号是相同的。这样的情况下,该用什么命令或者说怎么做才可以很好的让这两个文件同步起来呢?

谢谢你的回答!

以下是引用merry在2008-1-24 8:41:00的发言:

那个eco.err的内容是说:每一个信号的连接必须要有不少于两个的网络.所以只有一个讯号的网络全部删除掉了.______当然,删除的全部都是BGA IC连接出来的信号,因为这个IC在PCB库里找不到。

因为我一直改元件,后面把IC PIN改为数字的就OK了。所以,那个错误的文件我也就没有了。但意思就是我上面说的,可以肯定是IC PIN脚定义的问题.

再请教LZ一个问题.关于两个文件同步的:

比如现在我手头有一个原理图文件,DRC, Create Netlist都OK.我还有一个PCB文件,此PCB文件里的元件,布线什么的基本上跟我此原理图很相似,但他们的命名不一样,以及网络名也有些不一样,比如在原理图里叫U1,在PCB里面是叫7300.当然元件,封装以及接线都是对应的,也就是说哪个元件出来该接什么讯号是相同的。这样的情况下,该用什么命令或者说怎么做才可以很好的让这两个文件同步起来呢?

谢谢你的回答!

把pcb里面的7300的ref通过eco模式 改为U1,

感觉我总是不能很清楚的表达自己的意思.

我想要的这种同步是:可以让我现有PCB文件已布好的部分可以保持不变。

因为我现在ECO过去元件都是跑一堆去了.线也已经没有,只剩鼠线.跟我import一个新的PCB文件一样.这不是我要的结果。

以下是引用merry在2008-1-24 10:36:00的发言:

感觉我总是不能很清楚的表达自己的意思.

我想要的这种同步是:可以让我现有PCB文件已布好的部分可以保持不变。

因为我现在ECO过去元件都是跑一堆去了.线也已经没有,只剩鼠线.跟我import一个新的PCB文件一样.这不是我要的结果。

我知道你所说的意思,原理图和pcb的器件名字一样,decal也对,除非时网路名字改了,要不走线时不会丢的

有同事做了个小板,在阻焊层画铜,是想把铜皮露出来做焊盘用的,但是板厂却没把铜做出来,有时在阻焊层画粗一点2D线板厂也把铜皮露出来(铺过铜的),请问板厂根据什么露出铜还是不露,还是不上铜的?

以下是引用xfcy在2008-1-24 13:45:00的发言:

有同事做了个小板,在阻焊层画铜,是想把铜皮露出来做焊盘用的,但是板厂却没把铜做出来,有时在阻焊层画粗一点2D线板厂也把铜皮露出来(铺过铜的),请问板厂根据什么露出铜还是不露,还是不上铜的?

露铜的区域是做在soldmask层的(分soldmasktop soldmaskbot)不论是铜皮还是2dline 、text。只要放在sold层,就是要露铜的,top层想露铜 就要把区域放在soldmasktop,bottom层要放在soldmaskbottom,不要放错层了,像你说的“把铜皮露出来做焊盘用的,但是板厂却没把铜做出来,”这种情况,先确认自己放的层是否正确,出的gerber是否正确

关键是gerber的正确,板厂是按gerber做板的,如果都没有问题,那就是板厂的问题了,不过根据我的经验,板厂出错的几率很小,除非板厂很烂很烂很烂,,,,如果让你们碰上了,你们就可以买彩票了,呵呵

放的层是正确的,但是gerber不是我们出的,我们都是直接给板厂PCB文件的。

以下是引用xfcy在2008-1-25 14:57:00的发言:

放的层是正确的,但是gerber不是我们出的,我们都是直接给板厂PCB文件的。

呵呵,那就找板厂赔偿吧,

顶贴排序

呵呵,好久没有做过内层分割的板子了,不知道是不是说的下面两种情况

内层分割

这种直接用 pour manager的flood就可以铺铜了

直接铺铜

两者都可以铺铜的,的二种比较麻烦一些,先用flood,net2会铺上,net1和net3不会铺,就需要选中shap,右键 flood来铺铜,但是一执行pour manager 里面的flood ,net1和net3就会没有铺铜,从新执行前面的动作想问下小编,你的层都是设的Split/mixed属性吗?你的铜框是用Copper\Plane area\Hatch中的哪个画的呀?你说的这两种我都不能实现。

看了上面各位朋友的讨论,收获不少。3Q !