请教高手:allego 的电源和地布线问题

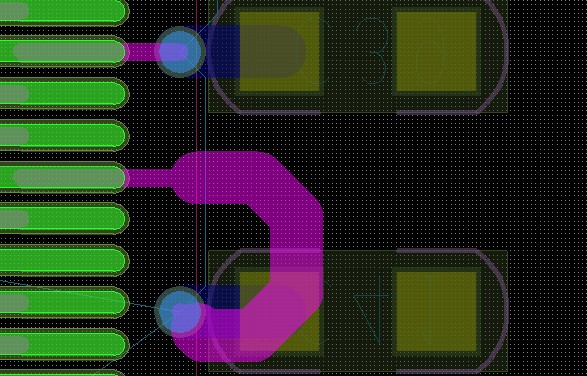

2、对于IC的电源引脚接去耦电容的线宽问题:我想让去耦电容先出粗一点的线,到IC引脚时再用较小的线宽接到IC引脚上,用了下neck模式布线不行,用区域规划来限制,感觉又太繁琐,还有什么好的处理方法呢,望高手给点建议。

软件速度的问题涉及很多方面,在一定程度上,禁用opengl、禁用shape的smooth、优化规则定义等可以加速软件反应速度。

要达到你说布线要求,区域规则是最方便最直接的方式;分段布线也可以,可以通过设置快捷键在布线时快速地切换线宽;另外一个方法是用copy或subdrawing的方式拷贝电容或芯片的扇出(fanout)。

谢谢你。

设置布线规则后,用neck模式对电源信号布线,通不过规则检查,是不是电源和地信号不能用neck模式布线?

你说的分段布线,是不是就是neck模式布线呢?

学习了,很好

传输线的最小最大线宽是由规则定义的,规则违背不是neck模式引起的,而是规则设置本身的问题;线宽不是只能靠neck模式才能改变,在option栏就能改变线宽。

再请问你一个问题:在哪儿设置禁用opengl呢?禁用shape的smooth,没多少用,移动元件或布线还是很卡。还有个原因可能是C盘剩余容量太少,造成缓存不够。

三防漆路过,看过了

setup -> user preferences -> Display -> Opengl -> disable_opengl

谢谢。

但对电源,地网络布线还是非常卡

电源和地平面指定电源属性,而且设置为负片层试试。

感谢yshang!

再问个问题:电源分割的时候,能不能将两个相同网络的区直接用线连通?比如,现在画的板子,3.3V有几个孤立的分割区,直接用走线将它们连接,合理不?

感谢yshang!

再问个问题:电源分割的时候,能不能将两个相同网络的区直接用线连通?比如,现在画的板子,3.3V有几个孤立的分割区,直接用走线将它们连接,合理不?

请先去了解铺铜对于电源是起什么作用,电源布线又有什么样的要求,要达到什么样的效果。

然后要了解铜线和铜皮在大电流情况下的特性。

最后去了解你的板子电源的分布和配送情况。

这些都了解,你就可以知道在你的板子上3.3V是否可以用直线连接了。

谢谢 yshang

yshang,再问个问题,allegro布好线后,更新了下封装,造成原布好的线失效,出现网络连不上,这样的话又得重新布线了,怎么解决呢?要用sub-drawing吗?谢谢

更新了元件封装之后,靠近该元件封装的其他元件也发生变化,丝印信息错乱了

update symbols时,不要勾选Reset symbols text location and size

封装变了,布线连接不上不是很正常的事情?在原先的线头处重新连接即可。如果是封装变了导致布线或过孔悬空,从而被动态铜皮“吃掉”,在更新封装前,先把动态铜皮移动到板外,更新后再移动回来即可。

对于动态shape关掉实时更新功能,等完成布线后再一次性更新

谢谢,小编。

还有个问题,弄了好久还没解决。

就是:我想对电源层采用20H规则,把电源层内缩下,开始对电源和地铺铜的时候,显示是正常的,确实是内缩了的。但当我分割内电层后,电源层铺铜区边框就和route keepin重合了,这是怎么回事呢?

谢谢,小编。

还有个问题,弄了好久还没解决。

就是:我想对电源层采用20H规则,把电源层内缩下,开始对电源和地铺铜的时候,显示是正常的,确实是内缩了的。但当我分割内电层后,电源层铺铜区边框就和route keepin重合了,这是怎么回事呢?

不回答了,不建议遇到问题就直接问人要答案,这个问题你完全可以通过做一些尝试后自己解决。铺铜的方式无非就是手动绘制(包括copy添加)以及通过split plane添加,对铺铜区域的影响无非就是route keepout和anti etch,尝试几次就能知道哪一个的优先级高,对什么类型的铜皮有影响了。

小编,这些问题,是我尝试了好久,没解决,才问你的。谢谢小编

铺铜的方式无非就是手动绘制(包括copy添加)以及通过split plane添加,对铺铜区域的影响无非就是route keepout和anti etch,尝试几次就能知道哪一个的优先级高,对什么类型的铜皮有影响了。

很给力啊,谢谢!~

小编回答的这几点很到位。走线时候时时改变线宽最简单额