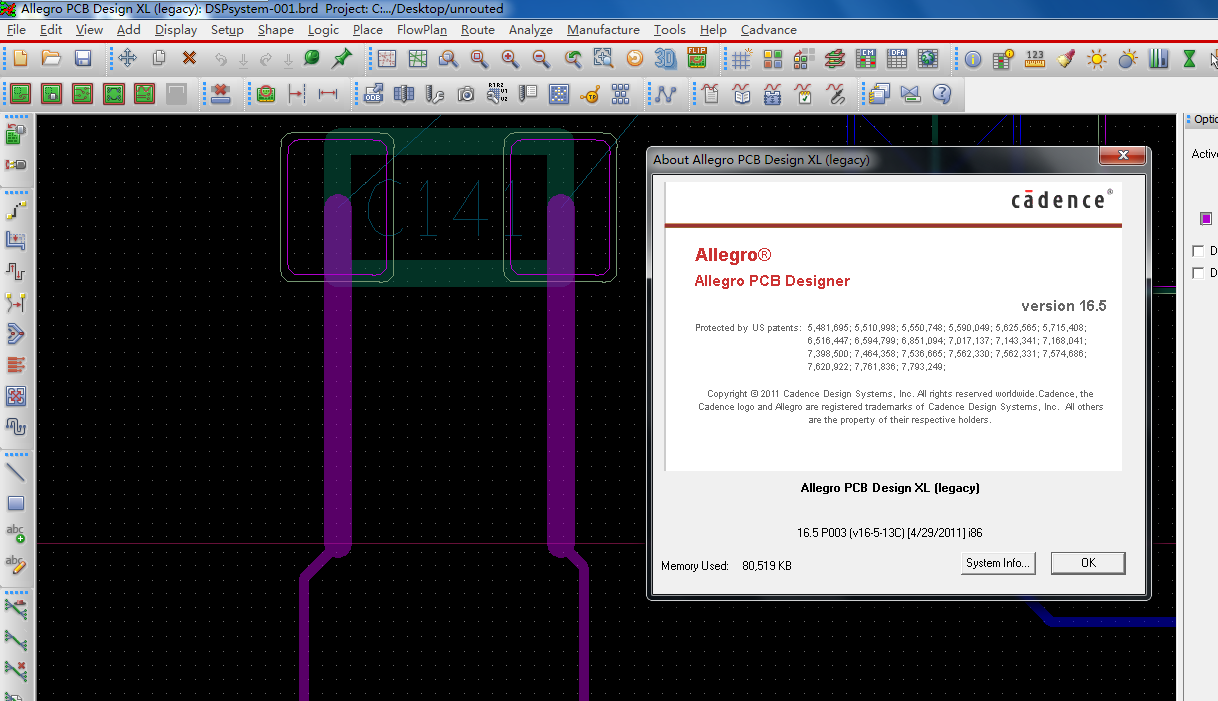

关于allegro 16.5 Constraint region设置问题

没有留意过16.5的constraint region有过什么设置上的变更,问题是否可以详细一点?

16.5的constraint region的设置,我不会,按照16.3的方法不行。大家是怎么设置的啊?

16.5 constraint region

顶顶!

先在Constraint Region层面下建shape(也就是region了)并命名,然后在Constraint Manager下面建规则,然后将规则分配给对应的Region(或者说是在此region的区域内什么样的网络会应用什么样的规则)。

从16.0以来,上述过程没有什么变化。而对于15.X版本,虽然规则不是在Constrain Manager下面设置,但是整个过程大同小异。我还真不明白小编的16.3的方法为什么在16.5不行,究竟是什么表现。

话多说几句,问问题还是建议把问题的前言后果表述清楚,像这个问题如果我来问,我会把我在16.3的Constraint Region设置操作步骤大致说一遍,然后对比16.3和16.5的drc效果,描述16.5在什么地方不正确。这样回答问题的人就能有的放矢,问题才有可能得到解决。

allegro 16.3规则设置方法详解

http://wenku.baidu.com/view/da33f919a8114431b90dd846.html?from=rec&pos=3&weight=13&lastweight=13&count=5

按照这个文档设置BGA区域规则,进入BGA区域后线宽变为6MIL,用CADENCE 16.3,走线进入BGA区域内线宽按照指定规则变为6MIL。同样方法用CADENCE16.5设置完成后,走线进入BGA区域内线宽不发生变化,依旧是10MIL.

为什么呢?是软件破解不完全?还是?

你提到的文档中描述的方法没有什么问题,16.5也是同样的方法设置。

如果你那里同时有16.3和16.5的环境,不妨试试分别用同样的方法,不同的版本(即16.3和16.5)打开同样的设计文件,然后按照文档中的方法设置好,再确认是否如你描述的16.3可以16.5不行;如果确实如此,再试试用16.3打开原先用16.5设置的文件(可以downrev),以及用16.5打开原先用16.3设置的文件,看看这时的情况怎么样。如果所有情况都是16.3可以或16.5不行,那基本上可以认定是16.5软件问题了,大概就是你所说的没有pj好吧,我这边的版本没有上述问题,16.5以来的补丁说明中也没有提到过相关修补。

谢谢,我试试哈

今天刚刚弄好了,谢谢yshang

无图无真相,解决问题感觉很爽

请帮忙说明解决问题方法

谢谢

感謝分享(~~~受用良多~~~3Q