走等长线的流程是怎么样的

时间:10-02

整理:3721RD

点击:

请教各位同行,一组BUS要走等长线时,思路是怎么样的?是否是先大概布一下线,再根据Constraint Manager做调整?望各位同行指点一下,谢谢~~

期待

同志们,发表一下意见也好啊

再顶一下吧

我覺得先對走等長線的網絡設置,設置長度一樣,在走線的時候超出這個長度的話,軟件是不會讓連接的。

那怎么完成

必須在你設置的長度的范圍之內才可以完成

因為你已經設置了長度

把这些net设成一个bus,然后再绝对长度里就可以设置最大最小值了

或者设成match group(CMGR里设,好像这么叫),然后在相对长度里面设。把一根做target,另外的设成正/负差多少就ok了

还可以用拓扑套用,这个就比较麻烦了。一般情况下上面两个足够了

http://www.cybernet.sh.cn/product.php?typeid=9&id=66

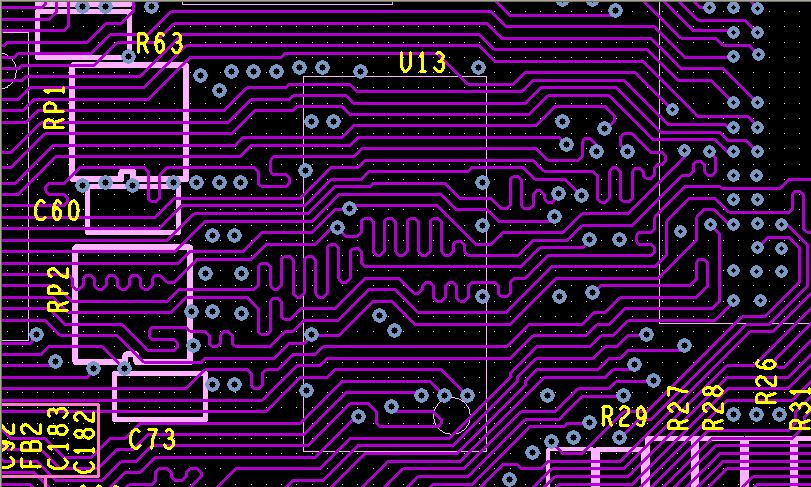

前些日子,我自己画了一组等长线,基本流程是这样的:设置好规则(方法和Rtiger_lp朋友的差不多)=》布线(线与线之间预留了一些空间)=》布线调整。整个画完,感觉好累。是不是我的方法不对?

布得不错啊,这种线就是比较麻烦

很漂亮

一般了。和电脑主板的走线比起来还差不少。这种布线真的感觉很累,应该有更好的布线技巧。欢迎同志们讨论。

好

等长还要别忘记加上bound length

看看

学习了,等长线还是不太容易呀

额定电压:250V