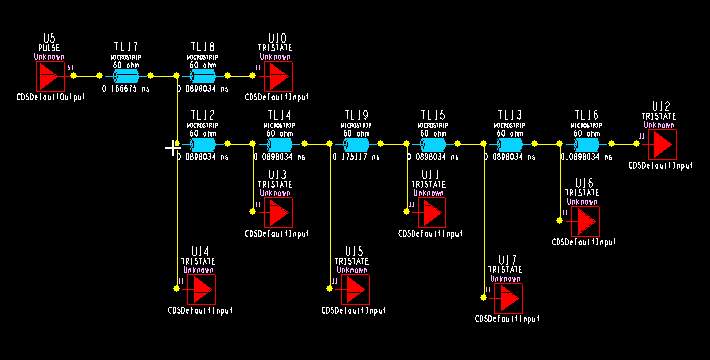

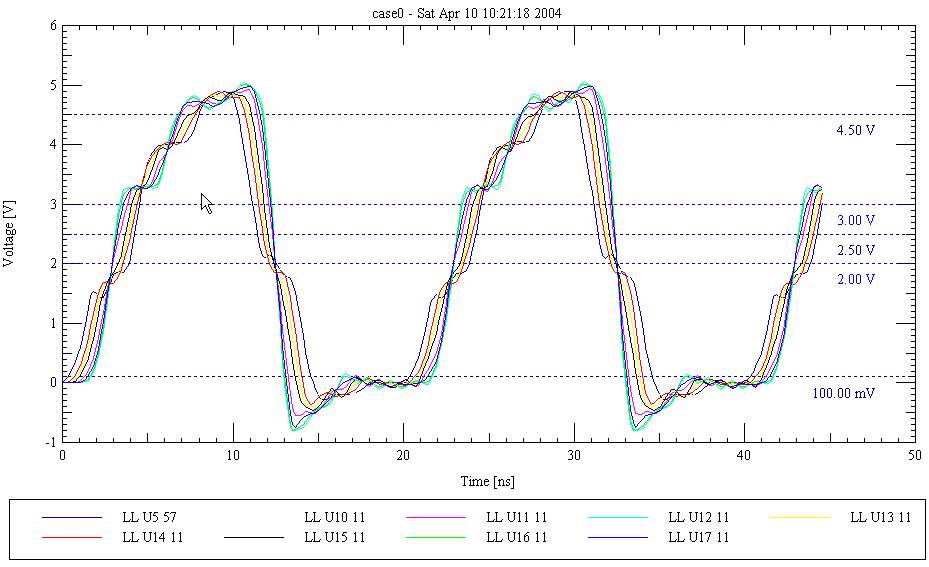

这是我生成的拓卜结构和仿真波形图,我试好几种方法,但是总是不能达到要求。

这是我生成的拓卜结构和仿真波形图,我试好几种方法,但是总是不能达到要求。

我想询问,再不改变芯片位置的前提下,有没有好的方法修改其拓卜结构,使其优化波形?

菊花链走线结构,芯片分得太开,所以波形是这样

解决方法:1. 采用T型结构,即走到中间,然后再分开两路,每边各接4个芯片

2. 如果一定要用串联的菊花链结构,尽量缩短芯片之间的距离,最好保证第一个接受芯片到最后一个接受芯片的距离在驱动芯片到最后一个接受芯片总长度的1/3之内。

谢谢

小编

鸣哥,能讲讲2为什么吗?

我简单地分析一下这个波形和走线结构:

关键知识点:

各负载的电压波形是入射信号和反射信号的叠加

这种情况下,负载阻抗较大,源端阻抗较小,所以负载端发射系数为+(会提高信号幅度),源端反射系数为-(降低信号幅度)

下面可以分析出的几个结果:

1。为什么边沿会出现台阶?--------因为终端和源断的反射,而反射波的传输是需要一定时间的,所以离驱动芯片最近的负载反而最后一个达到最高幅值(反射波传得最晚)。

2。为什么上升沿波形有好几处台阶,而下降沿只有一个?--------因为下降沿快,上升沿慢,而第一段线长很短,所以前面几个负载的反射很快到源端负反射叠加,对于上升沿来说,上升到一半的时候,反射就过来了,二次反射(幅度为负)叠加上来,所以出现一个下凹的台阶。而对于下降沿,由于很快,反射过来的时候,下降沿已经结束了,所以边沿没有二次反射的叠加。

分析出这两点,就知道怎么解决了:

把进入第一个负载之前的线加长~~比如设置为0.6ns以上,这样就可以发现,上升沿没有那么多反射台阶了。

将芯片靠近走,特别是U15和U11之间的那段0.17ns的走线变短,就可以发现所有的芯片波形重合的比较好了~~

这两点综合在一起,就可以大概推导出我前面说菊花链拓补结构的1/3原则

强!

鸣哥,厉害

讲解的明了易懂,辛苦了!

厉害啊!

有人知道鸣哥的资历和大致的工作历程么?

让我们这些后辈瞻仰瞻仰,同时也有迹可循啊!

强就一个字啊!

强啊

解答的很好。

弱弱地问一句,鸣哥,不是说菊花链的拓扑结构比T型拓扑结构好吗?