怎样仿真串扰(crosstalk)

时间:10-02

整理:3721RD

点击:

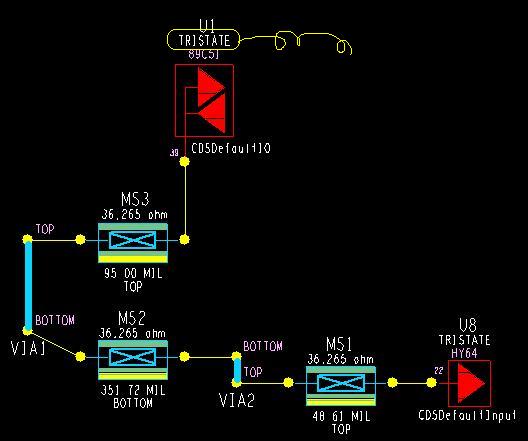

在PCB图中,只能提取出一个网络走线的拓扑图,

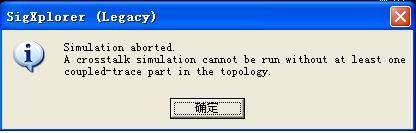

但是在仿真串扰的时候,提示

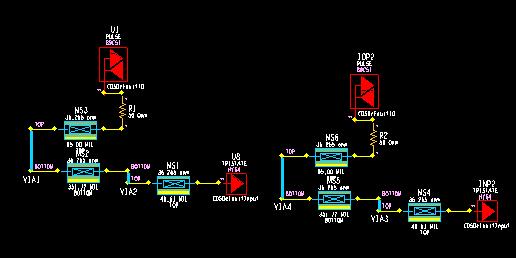

在旁边画好另外一个网络的拓扑图后:

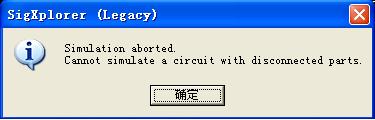

再仿真,出现下面的提示

请问该怎么办?有大侠做过allegro串扰的仿真吗,能够赐教一下,谢谢!

同问哦~

不能用拓扑做这个仿真

可以在论坛里面搜索一下的,挺多人讨论过这个问题了

能够用,问题已经解决了,在拓扑图中Edit-〉Add,选择Interconnect,里面Coupled-trace1等等,

这些就是PCB走线中相互靠近的线的拓扑图,可以定义Coupled-trace的长度(即走线靠近的长度,距离远了就没有必要考虑串扰了)等一些属性,然后在Messument里面就可以进行Crosstalk仿真了。

ding

小编说的拓扑其实不是走线的实际耦合情况了

怎么不是呢,我可以对这个Coupled-trace进行属性设置,制定实际的线宽,线长,间距,板子的介电常数,这些对于实际耦合情况描述的应该比较详细了吧

知道你说的意思,我的意思是这样做的话类似于前仿真了,仅仅是一种不精确的情况

我想什么前啊后的倒不是什么要值得注意的,关键是通过仿真来定好走线规则,在什么样的规则下串扰最小。

哪里有spb下载啊?!找不到啊

你这是加一个串扰模型,而不是加neighbure net同时激励

有理,你这样做根本就不是你PCB板上的实际的布线间的情况,加的只是一个模型.这问题还真头晕!