弱问一下退耦电容的位置

这样放置应该可以吧?

大家一般如何放置退耦电容的,退耦电容的地端是不是直接与芯片对应管脚的地连接在一起吧?

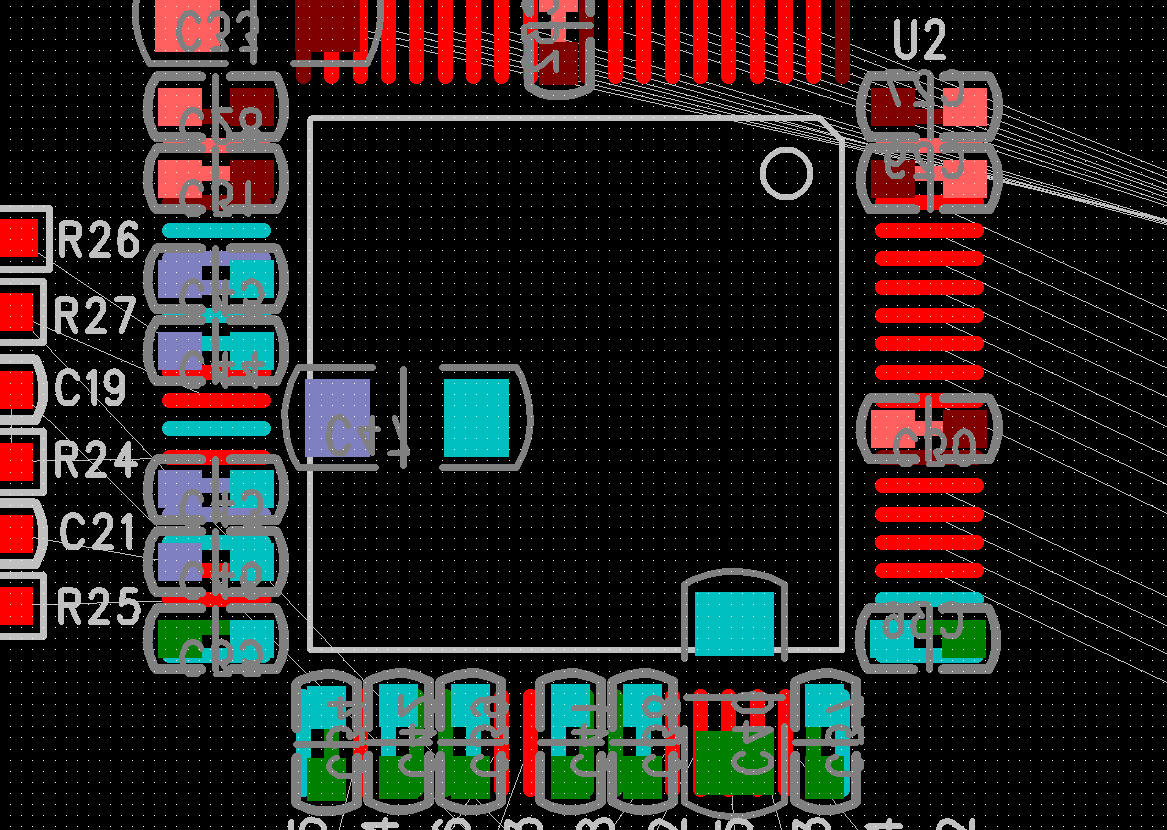

我大概这样布置了一下

那个最大的是10uf的

其他的都是0.1uf的电容,每个在就近的对应管脚处

那个10uf在在布局与走线是不是随便放个位置与0.1uf的电容之一连接上就可以了吗?

在一论坛上看到的:

【1】 不是。因为你的电源还是从外部引入的,所以要考虑人家的负载能力。

电容很大时候,通电瞬间的浪涌可能让电源过载。

除此之外,就是成本,空间之类的考虑。

最重要的是,别让别的工程师笑话,不能上无限多电容。

《它这里指的是不是那些有极性的电解电容吧?如果不是电解电容的话是不是就没有这个问题了?》

【2】其实电容放很多意义不大的。

你不可能把电容都集中在一个很小的区域内,之间肯定要导线连接,

这样一连接,电容的意义就不大了。

其实只要在靠近芯片电源管脚的地方安置足够容量的电容就差不多了。

还有就是不要选择同样容量的电容或者是一些电容容量是二、三等倍数关系的。

选择一些0.1uF的,一些0.01uF的,一些0.001uF的搭配着放效果会好些。

《我的理解是选一个大电容和一个小电容搭配的原因是,大电容有寄生电感效应,当频率较高的时候就类似一个大电阻,这些高频的信号就无法谢放,所以加个滤高频的小电容;但是这个大电容一般多指那些电解性质的电容吧?如果是具有非寄生电感的是不是就没这问题了?》

【3】那么如何合理的确定板上的电容值呢?

如果将选取的容值定为10u、0.1u、0.01u,

每种应该使用的个数应该怎么确定呢?

看要多高的要求了

精密电路的话要分析抑制那些频率,然后再选容值

《你说这个怎分析?是通过电源完整性仿真出来的效果吗?》