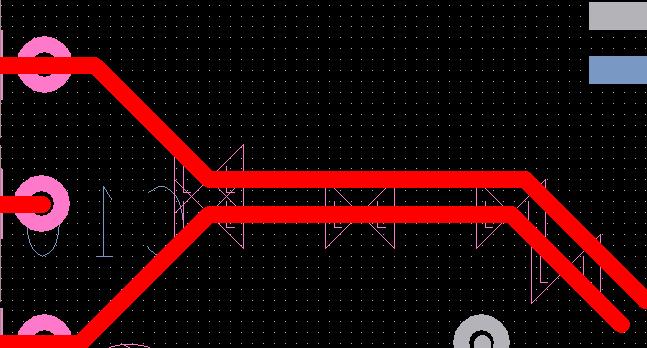

差分线对规则设置

LISTING: 1 element(s)

< DRC ERROR >

Class: DRC ERROR CLASS

Subclass: TOP

Origin xy: (42.1000 82.2000)

CONSTRAINT: Line to Line Spacing

CONSTRAINT SET: DEFAULT

CONSTRAINT TYPE: NET SPACING CONSTRAINTS

Constraint value: 0.16 MM

Actual value: 0.16 MM

- - - - - - - - - - - - - - - - - - - -

Element type: HORIZONTAL LINE SEGMENT

Class: ETCH

Subclass: TOP

part of a connect line

Part of Net Name: 100PHY_TPFIN

segment:xy (44.8674 81.8800) xy (42.1000 81.8800) width (0.1600)

- - - - - - - - - - - - - - - - - - - -

Element type: ODD-ANGLE LINE SEGMENT

Class: ETCH

Subclass: TOP

part of a connect line

Part of Net Name: 100PHY_TPFIP

segment:xy (42.1000 82.2000) xy (41.0550 83.2450) width (0.1600)

- - - - - - - - - - - - - - - - - - - -

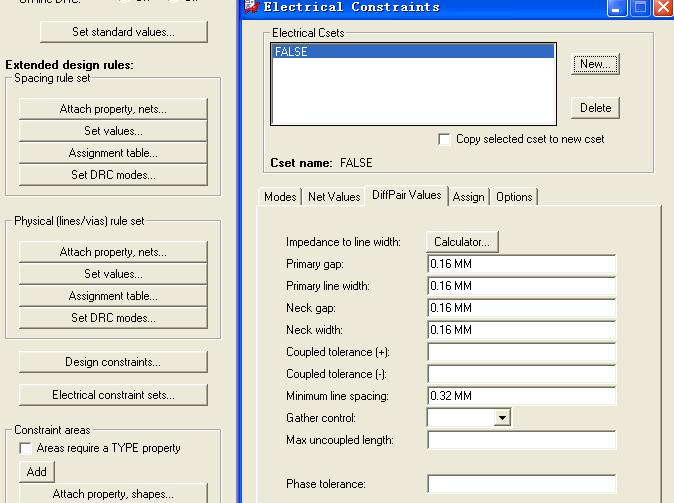

这些的关系如何,怎么设置

我的线宽1.6MM,一倍线距,如何才能不报错?

咋就没人说说呢?

添加 DIFFP_MIN_SPACE = 0.16 MM

0.32MM改为0.16MM

小编的帖子我一定顶

http://www.pcbbbs.com/viewthread.php?tid=107418