为什么FPGA引脚全都输出高电平

时间:10-02

整理:3721RD

点击:

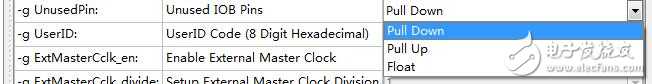

各位大神,我自己焊了一块FPGA的最小系统板,FPGA能下载程序,下载程序前就把unused pins设置为input tri-stated,但除了所有的引脚都输出高电平是什么状况?确认没有虚焊,电源、jtag都没问题。

什么环境,ise是这样的

altera 的QuartusII环境

没用过,但是你设置的是三态的话高电平也没有错啊

也就是说。那其实不是高电平而是高阻态?FPGA没配置成功?

你设置的不就是三态么,我猜相当于ISE的float,除了所有的引脚都为高电平是啥意思?不用的为高电平正常啊,还是你有用的有信号的引脚也输出了高电平

ISE我也没用过,你的猜测我真不太清楚,但设置了输入三态之后引脚显示高阻态确实是正常现象,但我编的一个测试程序是用到的引脚输出应该是方波,但这个引脚用示波器观察还是高阻态这就纠结了。

那就是输出有问题啊,板子上有led没,你先直接assign给led给值看看输出正确不,如果输出正确再看时钟有没有问题,时钟正确再看复位有没有问题,先看这些吧

嗯,很有条理的建议,谢谢,我再看看

你好,请问,你的问题是怎么解决的?我现在也遇到这样的问题了

时钟怎么看?直接用示波器测有源晶振的输出吗?

没有焊过,这个不懂