为什么MH计数到5不停止还要继续计数呢

时间:10-02

整理:3721RD

点击:

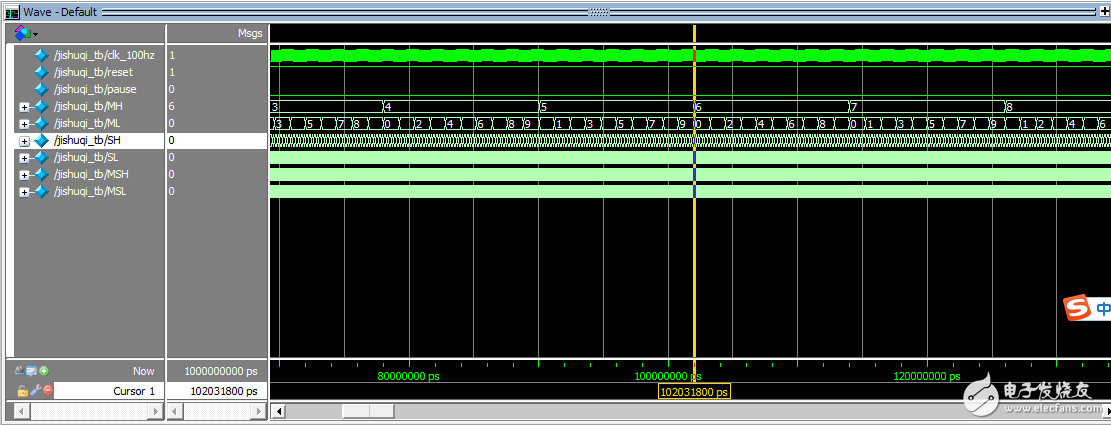

上面是数字跑表计数器模块仿真图,分十位MH计时到5后仍然继续计数,请大神指点这个问题怎么解决。

下面是程序:

module jishuqi(clk_100hz,reset,pause,MH,ML,SH,SL,MSH,MSL);

input clk_100hz,reset,pause;

output reg [3:0]MH;

output reg [3:0]ML;

output reg [3:0]SL;

output reg [3:0]SH;

output reg [3:0]MSL;

output reg [3:0]MSH;

reg cnt_ms;

reg cnt_s;

always@(posedge clk_100hz or negedge reset)

begin

if(!reset)

begin

MSL 5)就好了 但是不懂为什么这样改就行了

是不是频率有偏差?或者没清零,可能不能每次正好都是5

不改的话直接计数到15 一直是这样 改了就计数到5 不懂为什么