一个关于quartus ii 中仿真的问题,功能仿真准确,为什么门级仿真就烂的一塌糊涂

时间:10-02

整理:3721RD

点击:

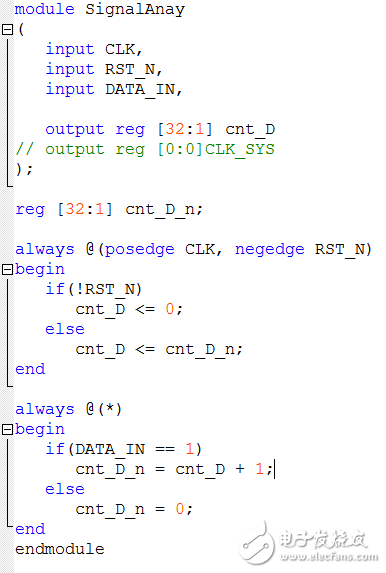

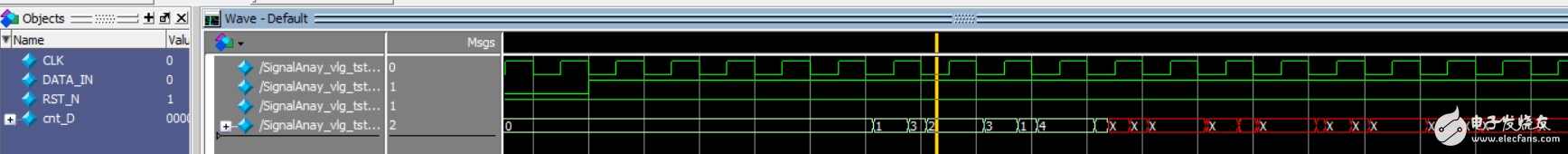

我是学了fpga没多久,写了一个小程序,在信号DATA_IN高电平时就开始计数,低电平时就归零,50MHz的参考时钟,功能仿真准确,但是门级仿真就是一开始有一些数值而且不对,后面就全部都是xxxxxx,我看着代码也没有哪里不对啊。求论坛有大神的教教我,真的很郁闷啊,到底哪里弄错了,也可能是很低级的错误。请各位大侠指教附图

程序

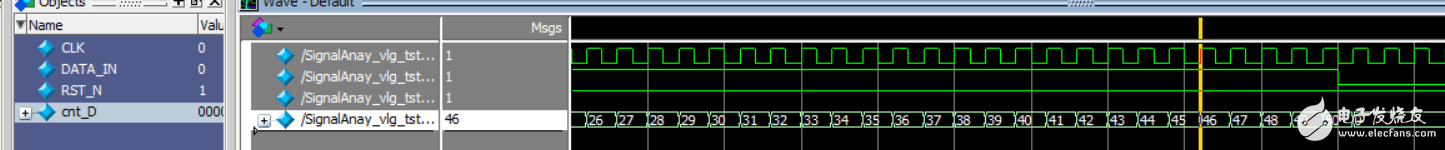

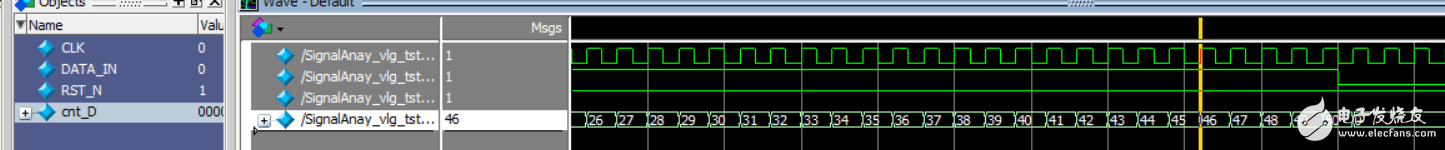

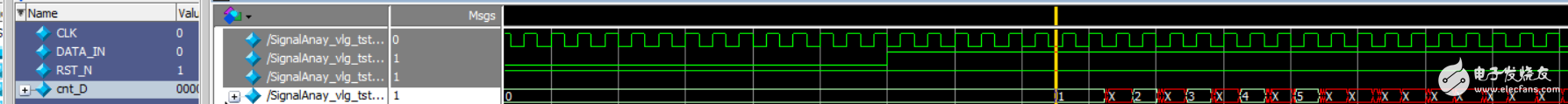

功能仿真

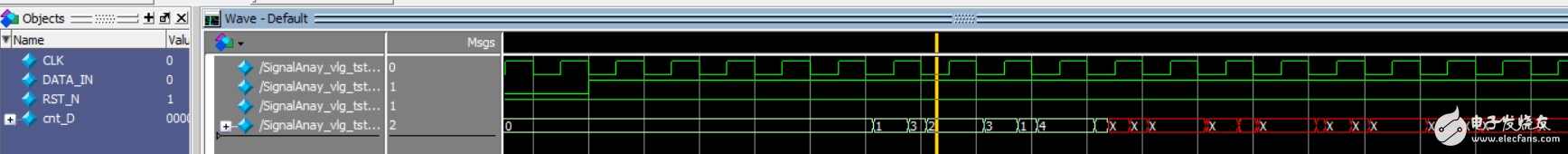

时序仿真

程序

功能仿真

时序仿真

第一,门级仿真就是功能仿真,没有区别;

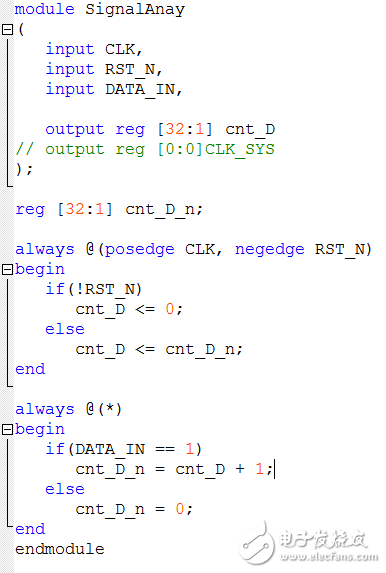

第二,你把第二个always@(*),改成always@(posedge CLK or negedge RST_N)再试试。

哦哦,那就是时序仿真和门级仿真,试了一下你说的,结果还是一样错的,

一般都是功能仿真加时序约束,不用后仿!

为什么不用后仿真,后仿真如果都不成功,那直接调试肯定出不来啊,看了一些关于TimeQuest的时序约束,还是不知道该怎么去用,怎么加时序约束才是好的

因为后仿意义不大啊,都是估算的触发器延时,真正到板子上的延时仿真器也不知道啊,所以功能仿真就行,那怎么保证加上触发器延时以后功能正常呢,这就是时序约束要干的事了,时序约束保证每个触发器的建立时间和保持时间都要满足,否则就会出现时序报红,报红的时序你就要优化代码了!如果不报红就说明加上了触发器延时和你功能仿真时一样的了!

第二个always块,中if(data_in==1),cnt_d_n<=cnt_d_n+1;而不是cnt_d_n<=cnt_d+1;

这样啊 也就是后仿真没什么实际意义,关于时序约束我再去看看,可是你觉得我的代码还需要哪些优化呢,我实在看不出了。

always @(*) 就是所有敏感条件都进入判断,就是所以if语句中判断的还有等号右边的变量变化的时候都会进入判断,

你第一个always块里用cnt_n改变cnt 又在第二个块里用cnt改变cnt_n 当然会有问题了

这种写法是我看教学视频时,视频里面的写法,因为功能仿真是正确的,所以这样写功能是对的,只是时序方面可能会有些问题,但是不是很清楚