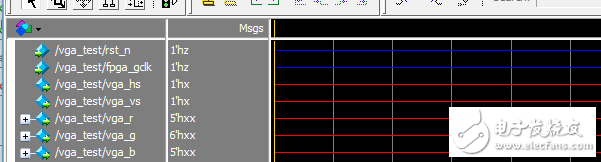

ISE联合Modelsim仿真波形为什么出现红线和蓝线?

如图。然而下载到开发板可以正常运行,网上说是要添加复位信号,请问怎样添加复位?

如图。然而下载到开发板可以正常运行,网上说是要添加复位信号,请问怎样添加复位?testbech里面时钟和复位都没有设置啊,设置方法为

initial begin

// Initialize Inputs

rst_n = 0;

fpga_gclk = 0;

key1 = 0;

// Wait 100 ns for global reset to finish

#100;

rst_n = 1;

// Add stimulus here

end

always begin

#5 fpga_gclk = ! fpga_gclk;

end

module vga_test(

input rst_n,

input fpga_gclk,

output vga_hs,

output vga_vs,

output [4:0] vga_r,

output [5:0] vga_g,

output [4:0] vga_b,

input key1 //按键key1

);

parameter LinePeriod =1344; //行周期数

parameter H_SyncPulse=136; //行同步脉冲(Sync a)

parameter H_BackPorch=160; //显示后沿(Back porch b)

parameter H_ActivePix=1024; //显示时序段(Display interval c)

parameter H_FrontPorch=24; //显示前沿(Front porch d)

parameter Hde_start=296;

parameter Hde_end=1320;

//-----------------------------------------------------------//

// 垂直扫描参数的设定1024*768 60Hz VGA

//-----------------------------------------------------------//

parameter FramePeriod =806; //列周期数

parameter V_SyncPulse=6; //列同步脉冲(Sync o)

parameter V_BackPorch=29; //显示后沿(Back porch p)

parameter V_ActivePix=768; //显示时序段(Display interval q)

parameter V_FrontPorch=3; //显示前沿(Front porch r)

parameter Vde_start=35;

parameter Vde_end=803;

reg[10 : 0] x_cnt;

reg[9 : 0] y_cnt;

reg[15 : 0] grid_data_1;

reg[15 : 0] grid_data_2;

reg[15 : 0] bar_data;

reg[3 : 0] vga_dis_mode;

reg[4 : 0] vga_r_reg;

reg[5 : 0] vga_g_reg;

reg[4 : 0] vga_b_reg;

reg hsync_r;

reg vsync_r;

reg hsync_de;

reg vsync_de;

reg [15:0] key1_counter; //按键检测寄存器

wire vga_clk;

wire CLK_OUT1;

wire CLK_OUT2;

wire CLK_OUT3;

wire CLK_OUT4;

wire [12:0] bar_interval;

assign bar_interval = H_ActivePix[15: 3]; //彩条宽度=H_ActivePix/8

//----------------------------------------------------------------

////////// 水平扫描计数

//----------------------------------------------------------------

always @ (posedge vga_clk)

if(~rst_n) x_cnt <= 1;

else if(x_cnt == LinePeriod) x_cnt <= 1;

else x_cnt <= x_cnt+ 1;

//----------------------------------------------------------------

////////// 水平扫描信号hsync,hsync_de产生

//----------------------------------------------------------------

always @ (posedge vga_clk)

begin

if(~rst_n) hsync_r <= 1'b1;

else if(x_cnt == 1) hsync_r <= 1'b0; //产生hsync信号

else if(x_cnt == H_SyncPulse) hsync_r <= 1'b1;

if(~rst_n) hsync_de <= 1'b0;

else if(x_cnt == Hde_start) hsync_de <= 1'b1; //产生hsync_de信号

else if(x_cnt == Hde_end) hsync_de <= 1'b0;

end

//----------------------------------------------------------------

////////// 垂直扫描计数

//----------------------------------------------------------------

always @ (posedge vga_clk)

if(~rst_n) y_cnt <= 1;

else if(y_cnt == FramePeriod) y_cnt <= 1;

else if(x_cnt == LinePeriod) y_cnt <= y_cnt+1;

//----------------------------------------------------------------

////////// 垂直扫描信号vsync, vsync_de产生

//----------------------------------------------------------------

always @ (posedge vga_clk)

begin

if(~rst_n) vsync_r <= 1'b1;

else if(y_cnt == 1) vsync_r <= 1'b0; //产生vsync信号

else if(y_cnt == V_SyncPulse) vsync_r <= 1'b1;

if(~rst_n) vsync_de <= 1'b0;

else if(y_cnt == Vde_start) vsync_de <= 1'b1; //产生vsync_de信号

else if(y_cnt == Vde_end) vsync_de <= 1'b0;

end

assign vga_hs = hsync_r;

assign vga_vs = vsync_r;

assign vga_r = (hsync_de & vsync_de)?vga_r_reg:5'b00000;

assign vga_g = (hsync_de & vsync_de)?vga_g_reg:6'b000000;

assign vga_b = (hsync_de & vsync_de)?vga_b_reg:5'b00000;

assign vga_clk = CLK_OUT3; //VGA时钟频率选择65Mhz

pll pll_inst

(// Clock in ports

.CLK_IN1(fpga_gclk), // IN

.CLK_OUT1(CLK_OUT1), // 21.175Mhz for 640x480(60hz)

.CLK_OUT2(CLK_OUT2), // 40.0Mhz for 800x600(60hz)

.CLK_OUT3(CLK_OUT3), // 65.0Mhz for 1024x768(60hz)

.CLK_OUT4(CLK_OUT4), // 108.0Mhz for 1280x1024(60hz)

.RESET(0), // reset input

.LOCKED(LOCKED)); // OUT

// INST_TAG_END ------ End INSTANTIATI

//按钮处理程序

always @(posedge vga_clk)

begin

if (key1==1'b0) //如果按钮没有按下,寄存器为0

key1_counter<=0;

else if ((key1==1'b1)& (key1_counter<=16'hc350)) //如果按钮按下并按下时间少于1ms,计数

key1_counter<=key1_counter+1'b1;

if (key1_counter==16'hc349) //一次按钮有效,改变显示模式

begin

if(vga_dis_mode==4'b1101)

vga_dis_mode<=4'b0000;

else

vga_dis_mode<=vga_dis_mode+1'b1;

end

end

endmodule

主要程序如上

有testbench文件吗?

module vtf_vga_test;

// Inputs

reg rst_n;

reg fpga_gclk;

reg key1;

// Outputs

wire vga_hs;

wire vga_vs;

wire [4:0] vga_r;

wire [5:0] vga_g;

wire [4:0] vga_b;

// Instantiate the Unit Under Test (UUT)

vga_test uut (

.rst_n(rst_n),

.fpga_gclk(fpga_gclk),

.vga_hs(vga_hs),

.vga_vs(vga_vs),

.vga_r(vga_r),

.vga_g(vga_g),

.vga_b(vga_b),

.key1(key1)

);

initial begin

// Initialize Inputs

rst_n = 0;

fpga_gclk = 0;

key1 = 0;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

end

endmodule

能帮我看看激励代码怎么写吗

这个VGA程序,我主要想看行、场同步信号的波形

没细看,感觉没有激励怎么会有输出。把gglk弄上方波,复位也处理一下弄成一段之间后不再复位。

咋不让他自己写呢,一句半句也是进步呢,你这样给他了他想的又少了

谢谢,我弄明白了