基于FPGA的电子日历设计——闰年的判断

时间:10-02

整理:3721RD

点击:

本人菜鸟一个,要设计一款基于FPGA的电子日历,利用verilog语言编写计时程序的时候,闰年的判断总是出问题,找不到解决方案,求大神指导!

代码:

module year(cn5,y,cn6,rst_n);

input cn5,rst_n; //cn5,月向年的进位符

output[15:0] y;

output cn6;

reg[15:0] y;

wire cn6;

parameter a=1;

parameter b=0;

assign cn6=(((y[15:0]%4==0)&&(y[15:0]%100!=0))||(y[15:0]%400==0))? a:b; //闰年标志位

always@(posedge cn5 or negedge rst_n)

begin

if(!rst_n)

y[15:0]=16'b0001_1001_1001_0100; //复位时显示1994年

else

begin

if(y[3:0]>=4'd9) begin

if(y[7:4]>=4'h9) begin

if(y[11:8]>=4'h9) begin

if(y[15:12]>=4'd9)

y[15:0]=16'b0001_0000_0000_0000;

else

begin

y[11:0]=0;

y[15:12]=y[15:12]+1;

end end

else

begin

y[7:0]=0;

y[11:8]=y[11:8]+1;

end end

else

begin

y[3:0]=0;

y[7:4]=y[7:4]+1;

end

end

else

y[3:0]=y[3:0]+1;

end

end

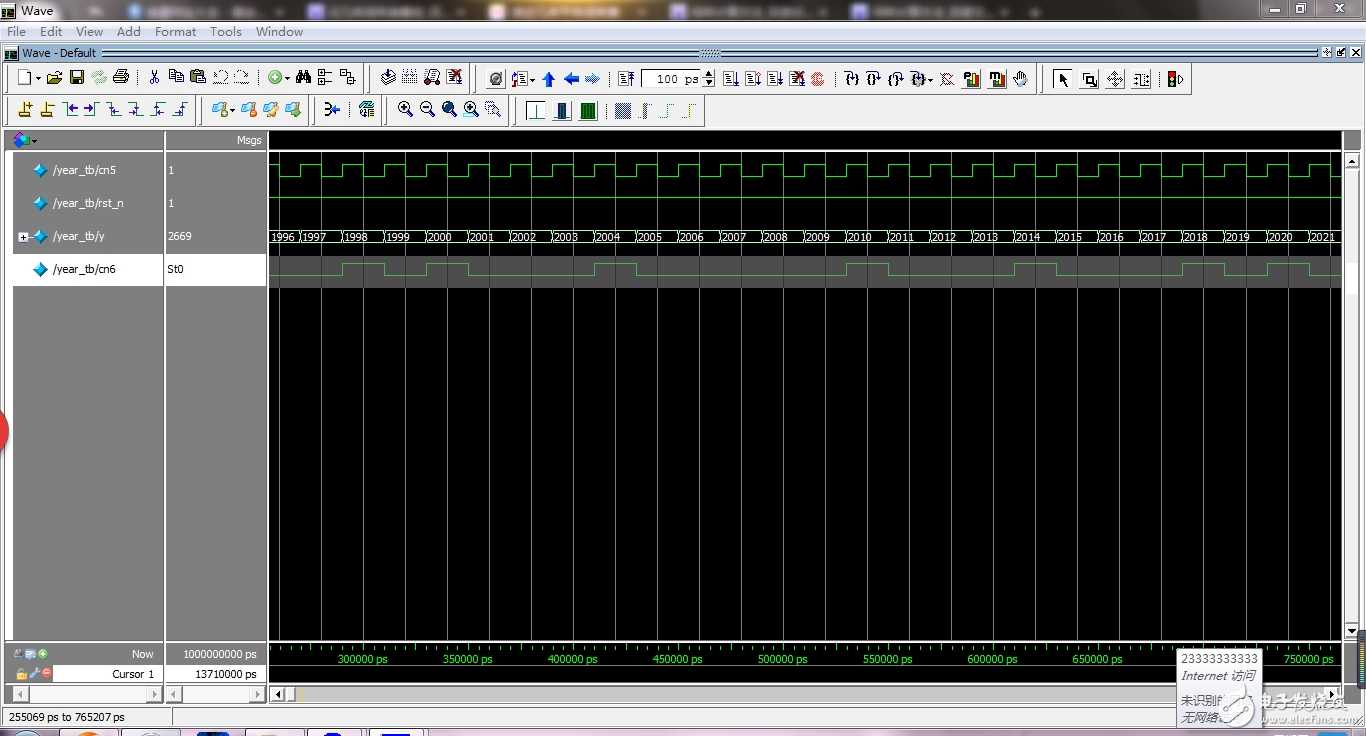

endmodule仿真图如下:

代码:

module year(cn5,y,cn6,rst_n);

input cn5,rst_n; //cn5,月向年的进位符

output[15:0] y;

output cn6;

reg[15:0] y;

wire cn6;

parameter a=1;

parameter b=0;

assign cn6=(((y[15:0]%4==0)&&(y[15:0]%100!=0))||(y[15:0]%400==0))? a:b; //闰年标志位

always@(posedge cn5 or negedge rst_n)

begin

if(!rst_n)

y[15:0]=16'b0001_1001_1001_0100; //复位时显示1994年

else

begin

if(y[3:0]>=4'd9) begin

if(y[7:4]>=4'h9) begin

if(y[11:8]>=4'h9) begin

if(y[15:12]>=4'd9)

y[15:0]=16'b0001_0000_0000_0000;

else

begin

y[11:0]=0;

y[15:12]=y[15:12]+1;

end end

else

begin

y[7:0]=0;

y[11:8]=y[11:8]+1;

end end

else

begin

y[3:0]=0;

y[7:4]=y[7:4]+1;

end

end

else

y[3:0]=y[3:0]+1;

end

end

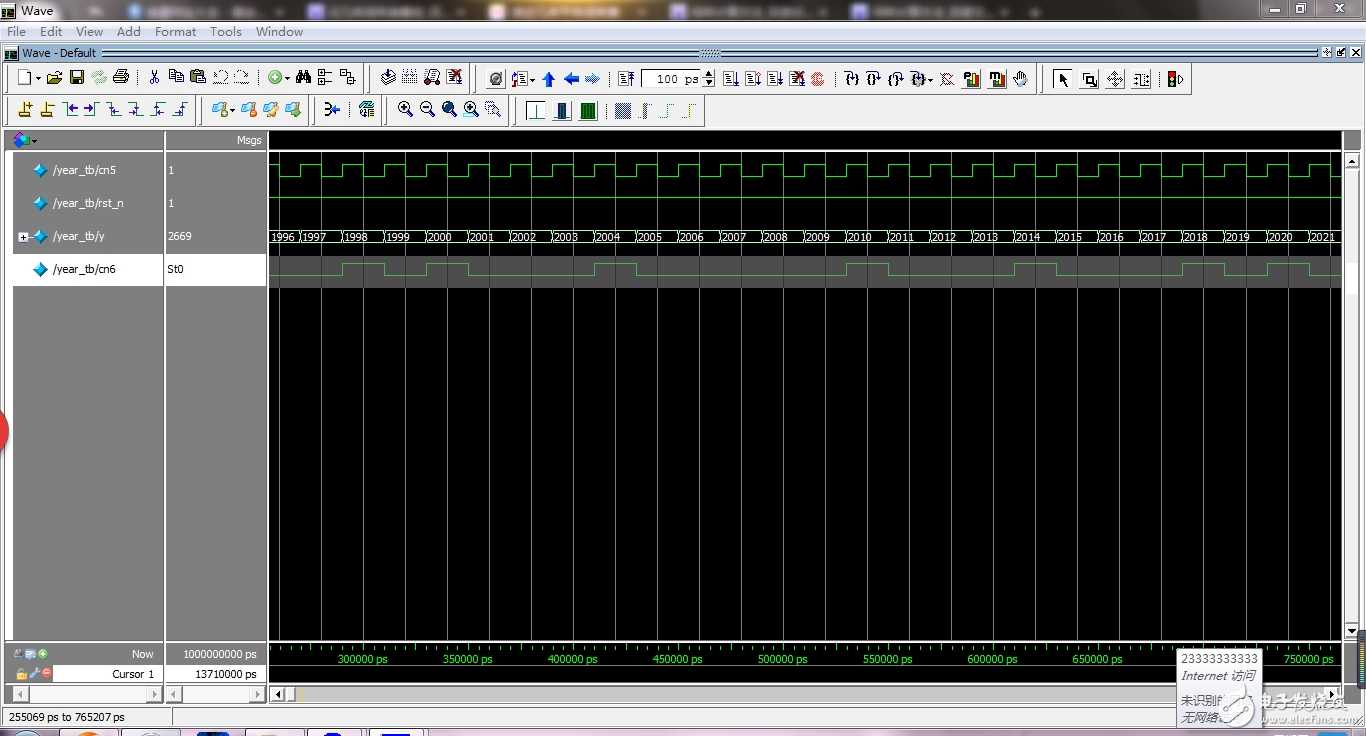

endmodule仿真图如下:

学习/学习/学习