stm32与fpga的spi通信小讨论

时间:10-02

整理:3721RD

点击:

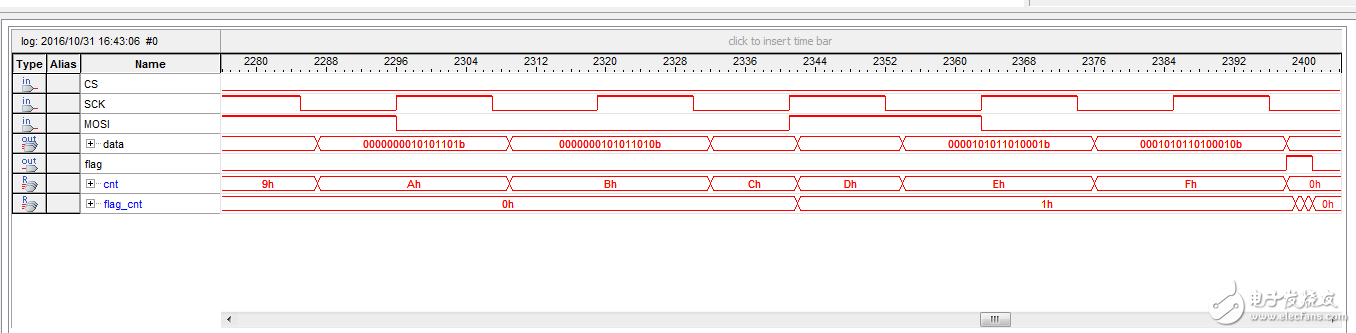

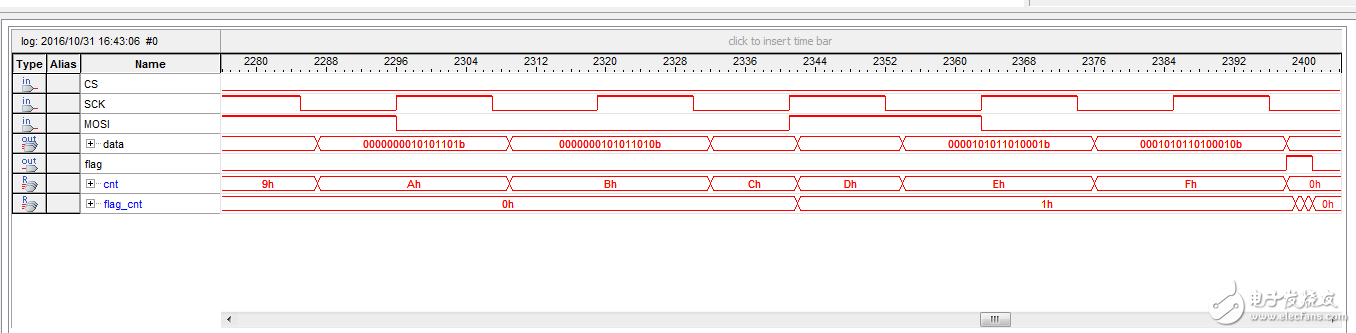

用stm32给fpga发送数据,然后用signaltap观察,发现数据和标志位flag有时候会出错,然后在signaltap中发现了错误的源头,如图

这两张分别是数据和计数器cnt在某个时刻出现多一个数据采集的情况,然后程序中cnt是被设计成在SCK的下降沿才加1,由图可以看到cnt出现了误操作,从而导致后面出问题。想问一下,在线调试时,cnt这种误操作是怎么产生的?有什么好的解决办法没有

这两张分别是数据和计数器cnt在某个时刻出现多一个数据采集的情况,然后程序中cnt是被设计成在SCK的下降沿才加1,由图可以看到cnt出现了误操作,从而导致后面出问题。想问一下,在线调试时,cnt这种误操作是怎么产生的?有什么好的解决办法没有

这两张分别是数据和计数器cnt在某个时刻出现多一个数据采集的情况,然后程序中cnt是被设计成在SCK的下降沿才加1,由图可以看到cnt出现了误操作,从而导致后面出问题。想问一下,在线调试时,cnt这种误操作是怎么产生的?有什么好的解决办法没有

这两张分别是数据和计数器cnt在某个时刻出现多一个数据采集的情况,然后程序中cnt是被设计成在SCK的下降沿才加1,由图可以看到cnt出现了误操作,从而导致后面出问题。想问一下,在线调试时,cnt这种误操作是怎么产生的?有什么好的解决办法没有

为什么你觉得是调试的时候导致的呢,你的问题不是很清楚

就是调试的时候出现的,仿真的时候没问题

就是调试的时候出现的,仿真的时候没问题

不知道你定义的变量nege是什么含义,你看一下第二张图你圈出来的那个地方正好是MOSI上升沿的地方,CS一直是低电平没有什么影响,唯一有可能的就是nege变量,你检查一下那个变量跟MOSI有什么关联吗?

不知道你定义的变量nege是什么含义,你看一下第二张图你圈出来的那个地方正好是MOSI上升沿的地方,CS一直是低电平没有什么影响,唯一有可能的就是nege变量,你检查一下那个变量跟MOSI有什么关联吗?

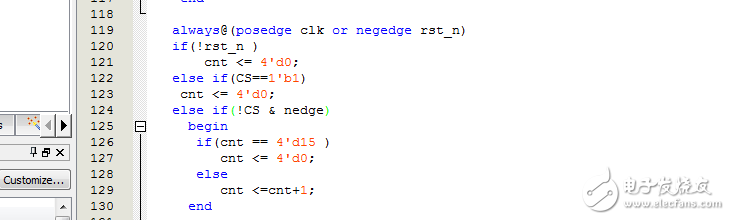

nedge是我设置的边沿检测信号,wire型,主要是检测sck的下降沿,检测到了就存mosi上的数据。

不要用边沿检测,直接用它下降沿驱动