求助!Verilog,AD转换测模拟电压输出到数码管显示,怎么错了!?

时间:10-02

整理:3721RD

点击:

求求帮帮忙,搞不明白哪里出错了,板子测试是8*8点阵全亮了,数码管只是第一位显示6,没反应。

分三个模块:顶层,AD控制,数码管显示。

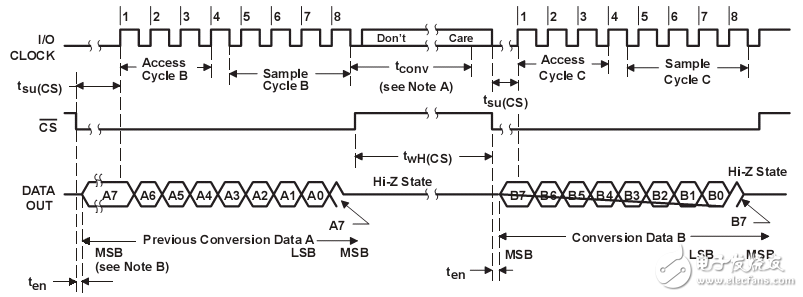

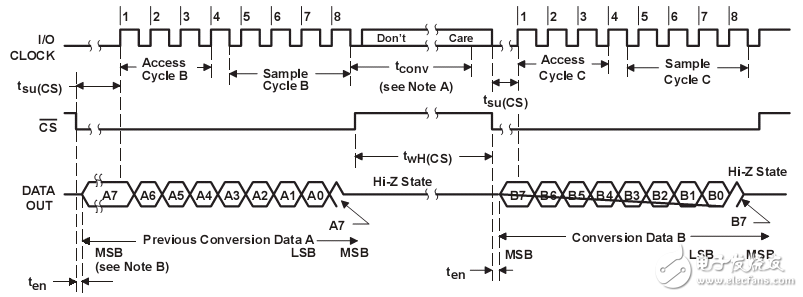

AD时序:

/**************************************************************************************

* 日期:2016年11月18日22:14:52 *

* *

* 功能:AD转化顶层模块 *

* 修改:2016年11月19日17:54:10 *

**************************************************************************************/

module AD_TOP_MODULE(

input CLK_48M, //系统时钟48MHZ

input RST_N, //系统复位端

input FROM_AD_DATA, //由AD芯片转化出来的数据

output TO_AD_CS, //输出到AD芯片的片选信号

output TO_AD_CLK, //输出到AD芯片的时钟小于1.1MHZ

output [7:0] DIG, //数码管数字段

output [3:0] SEL //数码管点亮位

);

//*************************************************************************************

wire [7:0] TO_DISPLAY_DATA; //输出到数码管现实模块的数据

//*************************************************************************************

// 调用AD控制模块

//*************************************************************************************

AD_CONTROL_MODULE AD_CONTROL_MODULE1(

.CLK_48M (CLK_48M), //系统时钟48MHZ

.RST_N (RST_N), //系统复位端

.FROM_AD_DATA (FROM_AD_DATA), //由AD芯片转化出来的数据

.TO_AD_CS (TO_AD_CS), //输出到AD芯片的片选信号

.TO_AD_CLK (TO_AD_CLK), //输出到AD芯片的时钟小于1.1MHZ

.TO_DISPLAY_DATA (TO_DISPLAY_DATA) //输出到数码管现实模块的数据

);

//*************************************************************************************

// 调用数码管显示模块

//*************************************************************************************。

DISPLAY_MODULE DISPLAY_MODULE1(

.CLK_48M (CLK_48M), //系统时钟48MHZ

.RST_N (RST_N), //系统复位端

.FROM_AD_CONTRL_DATA (TO_DISPLAY_DATA), //从AD控制模块输入的数据

.DIG (DIG), //数码管数字段

.SEL (SEL) //数码管点亮位

);

//*************************************************************************************

endmodule

分割-----------------------------------------------------------------------------------------------------------------

/*************************************************************************************

* 日期:2016年11月18日22:14:52 *

* 作者:黄志华 *

* 功能:AD控制模块 *

* 修改:2016年11月19日17:31:49 *

*************************************************************************************/

module AD_CONTROL_MODULE(

input CLK_48M, //系统时钟48MHZ

input RST_N, //系统复位端

input FROM_AD_DATA, //由AD芯片转化出来的数据

output reg TO_AD_CS, //输出到AD芯片的片选信号

output reg TO_AD_CLK, //输出到AD芯片的时钟小于1.1MHZ

output reg [7:0] TO_DISPLAY_DATA //输出到数码管现实模块的数据

);

//*************************************************************************************

parameter FSM_WAIT = 5'b00001; //1.5us

parameter FSM_DELAY = 5'b00010; //1/4*2=0.5us

parameter FSM_DATA = 5'b00100; //8*1/1.1=8*0.91us

parameter FSM_OVER = 5'b01000; //17us

parameter FSM_END = 5'b10000; //0.2us

parameter AD_CLK_TIME = 6'd44; //48M/1.1M<44

parameter AD_CLK_TIME_HALF = 6'd22; //一半的1.1MHZ

//*************************************************************************************

reg TO_AD_CS_N; //输出到AD芯片的片选信号

reg TO_AD_CLK_N; //输出到AD芯片的时钟小于1.1MHZ

reg [7:0] TO_DISPLAY_DATA_N; //输出到数码管现实模块的数据

reg [4:0] FSM_REG_CS; //状态机寄存器当前状态

reg [4:0] FSM_REG_NS; //状态机寄存器下一状态

reg [5:0] AD_CLK_TIME_CNT; //AD_CLK周期计数

reg [5:0] AD_CLK_TIME_CNT_N; //AD_CLK周期计数

reg [5:0] AD_CLK_TIME_COUNTER; //AD_CLK计数器

reg [7:0] FROM_AD_DATA_REG; //从接收AD芯片输入的8位数据

reg [7:0] FROM_AD_DATA_REG_N; //从接收AD芯片输入的8位数据

reg [7:0] STEADY_DATA; //从接收AD芯片输入的8位数据稳定的数据

reg [7:0] STEADY_DATA_N; //从接收AD芯片输入的8位数据稳定的数据

//*************************************************************************************

// 有限状态机FSM

//*************************************************************************************

always @(posedge CLK_48M)

begin

if(!RST_N) FSM_REG_CS<=1'b0; //当前状态赋值

else FSM_REG_CS<=FSM_REG_NS;

end

//*************************************************************************************

always @(*)

begin

case(FSM_REG_CS)

FSM_WAIT:begin if((AD_CLK_TIME_CNT==2)&&(AD_CLK_TIME_COUNTER==AD_CLK_TIME))

FSM_REG_NS=FSM_DELAY;

else FSM_REG_NS=FSM_REG_CS; end

FSM_DELAY:begin if((AD_CLK_TIME_CNT==1)&&(AD_CLK_TIME_COUNTER==AD_CLK_TIME))

FSM_REG_NS=FSM_DATA;

else FSM_REG_NS=FSM_REG_CS; end //下个状态赋值

FSM_DATA:begin if((AD_CLK_TIME_CNT==8)&&(AD_CLK_TIME_COUNTER==AD_CLK_TIME))

FSM_REG_NS=FSM_OVER;

else FSM_REG_NS=FSM_REG_CS; end

FSM_OVER:begin if((AD_CLK_TIME_CNT==19)&&(AD_CLK_TIME_COUNTER==AD_CLK_TIME))

FSM_REG_NS=FSM_END;

else FSM_REG_NS=FSM_REG_CS; end

FSM_END:begin if((AD_CLK_TIME_CNT==2)&&(AD_CLK_TIME_COUNTER==AD_CLK_TIME))

FSM_REG_NS=FSM_WAIT;

else FSM_REG_NS=FSM_REG_CS; end

default: FSM_REG_NS=FSM_WAIT;

endcase

end

//*************************************************************************************

// TO_AD_CLK波形生成

//*************************************************************************************

always @(posedge CLK_48M)

begin

if(!RST_N) TO_AD_CLK<=1'b0; //当前状态赋值

else TO_AD_CLK<=TO_AD_CLK_N;

end

//*************************************************************************************

always @(*)

begin

if(FSM_REG_CS!=FSM_DATA) TO_AD_CLK_N=0;

else if(AD_CLK_TIME_COUNTER==AD_CLK_TIME)

TO_AD_CLK_N=1; //下个状态赋值

else if(AD_CLK_TIME_COUNTER==AD_CLK_TIME_HALF)

TO_AD_CLK_N=0;

else TO_AD_CLK_N=TO_AD_CLK;

end

//*************************************************************************************

// TO_AD_CS波形生成

//*************************************************************************************

always @(posedge CLK_48M)

begin

if(!RST_N) TO_AD_CS<=1'b0; //当前状态赋值

else TO_AD_CS<=TO_AD_CS_N;

end

//*************************************************************************************

always @(*)

begin

case(FSM_REG_CS)

FSM_WAIT: TO_AD_CS_N=1;

FSM_DELAY: TO_AD_CS_N=0;

FSM_DATA: TO_AD_CS_N=0; //下个状态赋值

FSM_OVER: TO_AD_CS_N=1;

FSM_END: TO_AD_CS_N=1;

default: TO_AD_CS_N=1;

endcase

end

//*************************************************************************************

// AD_CLK周期计数

//*************************************************************************************

always @(posedge CLK_48M)

begin

if(!RST_N) AD_CLK_TIME_CNT<=1'b0; //当前状态赋值

else AD_CLK_TIME_CNT<=AD_CLK_TIME_CNT_N;

end

//*************************************************************************************

always @(*)

begin

if(FSM_REG_CS!=FSM_REG_NS) AD_CLK_TIME_CNT_N<=0;

else if(AD_CLK_TIME_COUNTER==AD_CLK_TIME_HALF) //下个状态赋值

AD_CLK_TIME_CNT_N=AD_CLK_TIME_CNT+1;

else AD_CLK_TIME_CNT_N=AD_CLK_TIME_CNT;

end

//*************************************************************************************

// 1.1MHZ计数

//*************************************************************************************

always @(posedge CLK_48M)

begin

if(!RST_N) AD_CLK_TIME_COUNTER<=0;

else if(AD_CLK_TIME_COUNTER==AD_CLK_TIME) //下个状态赋值

AD_CLK_TIME_COUNTER<=0;

else AD_CLK_TIME_COUNTER<=AD_CLK_TIME_COUNTER+1'b1;

end

//*************************************************************************************

// 输入数据移位寄存器

//*************************************************************************************

always @(posedge CLK_48M)

begin

if(!RST_N) FROM_AD_DATA_REG<=1'b0; //当前状态赋值

else FROM_AD_DATA_REG<=FROM_AD_DATA_REG_N;

end

//*************************************************************************************

always @(*)

begin //下个状态赋值

if((FSM_REG_CS==FSM_DATA)&&(AD_CLK_TIME_COUNTER==AD_CLK_TIME_COUNTER))

FROM_AD_DATA_REG_N={FROM_AD_DATA_REG[6:0],FROM_AD_DATA};

else FROM_AD_DATA_REG_N=FROM_AD_DATA_REG;

end

//*************************************************************************************

// 稳定输出数据

//*************************************************************************************

always @(posedge CLK_48M)

begin

if(!RST_N) TO_DISPLAY_DATA<=1'b0; //当前状态赋值

else TO_DISPLAY_DATA<=TO_DISPLAY_DATA_N;

end

//*************************************************************************************

always @(*)

begin

if(AD_CLK_TIME_CNT==8) TO_DISPLAY_DATA_N=FROM_AD_DATA_REG;

else TO_DISPLAY_DATA_N=TO_DISPLAY_DATA;

end

//*************************************************************************************

endmodule

/*************************************************************************************

* 日期:2016年11月18日22:14:52 *

* 作者:黄志华 *

* 功能:数码管显示模块 *

* 修改:2016年11月19日17:54:19 *

*************************************************************************************/

module DISPLAY_MODULE(

input CLK_48M, //系统时钟48MHZ

input RST_N, //系统复位端

input [7:0] FROM_AD_CONTRL_DATA, //从AD控制模块输入的数据

output reg [7:0] DIG, //数码管数字段

output reg [3:0] SEL //数码管点亮位

);

//************************************************************************************

parameter Numb0 = 7'b1000000;

parameter Numb1 = 7'b1111001;

parameter Numb2 = 7'b0100100;

parameter Numb3 = 7'b0110000;

parameter Numb4 = 7'b0011001; //数码管显示无点数字定义

parameter Numb5 = 7'b0010010;

parameter Numb6 = 7'b0000010;

parameter Numb7 = 7'b1111000;

parameter Numb8 = 7'b0000000;

parameter Numb9 = 7'b0010000;

//************************************************************************************

parameter SET_SEL0 = 4'b0111;

parameter SET_SEL1 = 4'b1011;

parameter SET_SEL2 = 4'b1101; //数码管分段点亮参数

parameter SET_SEL3 = 4'b1110;

//************************************************************************************

parameter FSM_1 = 1'b0; //状态1

parameter FSM_2 = 1'b1; //状态2

parameter COUNTER = 20'd100_000; //1/48*1000_000=20ms

//************************************************************************************

reg FSM_CS; //状态寄存器当前状态

reg FSM_NS; //状态寄存器下一状态

reg [1:0] TIME_COUNTER; //20ms计数器

reg [6:0] n1; //数码管显示整数部分寄存器

reg [6:0] n2; //数码管显示小数部分寄存器

//************************************************************************************

// 有限状态机FSM

//************************************************************************************

always @(posedge CLK_48M)

begin

if(!RST_N) FSM_CS<=1'b0;

else FSM_CS<=FSM_NS;

end

//************************************************************************************

always @(*)

begin

if(TIME_COUNTER==COUNTER) FSM_NS=FSM_CS+1'b1;

else FSM_NS=FSM_CS;

end

//************************************************************************************

// 显示设置

//************************************************************************************

always @(*)

begin

case(FSM_CS)

FSM_1:begin DIG[6:0]=n1;DIG[7]=1'b0;SEL=SET_SEL0; end

FSM_2:begin DIG[6:0]=n2;DIG[7]=1'b1;SEL=SET_SEL1; end

default:SEL=4'b1111;

endcase

end

//************************************************************************************

// 20ms计时

//************************************************************************************

always @(posedge CLK_48M)

begin

if(!RST_N) TIME_COUNTER<=1'b0;

else if(TIME_COUNTER==COUNTER)

TIME_COUNTER<=1'b0;

else TIME_COUNTER<=TIME_COUNTER+1'b1;

end

//************************************************************************************

// 数据转换

//************************************************************************************

always @(*)

begin

case(FROM_AD_CONTRL_DATA[7:2])

6'd0:begin n1=Numb0;n2=Numb0;end

6'd1:begin n1=Numb0;n2=Numb1;end

6'd2:begin n1=Numb0;n2=Numb1;end

6'd3:begin n1=Numb0;n2=Numb2;end

6'd4:begin n1=Numb0;n2=Numb2;end

6'd5:begin n1=Numb0;n2=Numb3;end

6'd6:begin n1=Numb0;n2=Numb3;end

6'd7:begin n1=Numb0;n2=Numb4;end

6'd8:begin n1=Numb0;n2=Numb4;end

6'd9:begin n1=Numb0;n2=Numb5;end

6'd10:begin n1=Numb0;n2=Numb5;end

6'd11:begin n1=Numb0;n2=Numb6;end

6'd12:begin n1=Numb0;n2=Numb6;end

6'd13:begin n1=Numb0;n2=Numb7;end

6'd14:begin n1=Numb0;n2=Numb7;end

6'd15:begin n1=Numb0;n2=Numb8;end

6'd16:begin n1=Numb0;n2=Numb8;end

6'd17:begin n1=Numb0;n2=Numb9;end

6'd18:begin n1=Numb0;n2=Numb9;end

6'd19:begin n1=Numb1;n2=Numb0;end

6'd20:begin n1=Numb1;n2=Numb0;end

6'd21:begin n1=Numb1;n2=Numb1;end

6'd22:begin n1=Numb1;n2=Numb1;end

6'd23:begin n1=Numb1;n2=Numb2;end

6'd24:begin n1=Numb1;n2=Numb2;end

6'd25:begin n1=Numb1;n2=Numb3;end

6'd26:begin n1=Numb1;n2=Numb3;end

6'd27:begin n1=Numb1;n2=Numb4;end

6'd28:begin n1=Numb1;n2=Numb4;end

6'd29:begin n1=Numb1;n2=Numb5;end

6'd30:begin n1=Numb1;n2=Numb5;end

6'd31:begin n1=Numb1;n2=Numb6;end

6'd32:begin n1=Numb1;n2=Numb6;end

6'd33:begin n1=Numb1;n2=Numb7;end

6'd34:begin n1=Numb1;n2=Numb7;end

6'd35:begin n1=Numb1;n2=Numb8;end

6'd36:begin n1=Numb1;n2=Numb8;end

6'd37:begin n1=Numb1;n2=Numb9;end

6'd38:begin n1=Numb1;n2=Numb9;end

6'd39:begin n1=Numb2;n2=Numb0;end

6'd40:begin n1=Numb2;n2=Numb0;end

6'd41:begin n1=Numb2;n2=Numb1;end

6'd42:begin n1=Numb2;n2=Numb1;end

6'd43:begin n1=Numb2;n2=Numb2;end

6'd44:begin n1=Numb2;n2=Numb2;end

6'd45:begin n1=Numb2;n2=Numb3;end

6'd46:begin n1=Numb2;n2=Numb3;end

6'd47:begin n1=Numb2;n2=Numb4;end

6'd48:begin n1=Numb2;n2=Numb4;end

6'd49:begin n1=Numb2;n2=Numb5;end

6'd50:begin n1=Numb2;n2=Numb5;end

6'd51:begin n1=Numb2;n2=Numb6;end

6'd52:begin n1=Numb2;n2=Numb6;end

6'd53:begin n1=Numb2;n2=Numb7;end

6'd54:begin n1=Numb2;n2=Numb7;end

6'd55:begin n1=Numb2;n2=Numb8;end

6'd56:begin n1=Numb2;n2=Numb8;end

6'd57:begin n1=Numb2;n2=Numb9;end

6'd58:begin n1=Numb2;n2=Numb9;end

6'd59:begin n1=Numb3;n2=Numb0;end

6'd60:begin n1=Numb3;n2=Numb0;end

6'd61:begin n1=Numb3;n2=Numb1;end

6'd62:begin n1=Numb3;n2=Numb1;end

6'd63:begin n1=Numb3;n2=Numb2;end

default:SEL=4'b1111;

endcase

end

//************************************************************************************

endmodule

分三个模块:顶层,AD控制,数码管显示。

AD时序:

/**************************************************************************************

* 日期:2016年11月18日22:14:52 *

* *

* 功能:AD转化顶层模块 *

* 修改:2016年11月19日17:54:10 *

**************************************************************************************/

module AD_TOP_MODULE(

input CLK_48M, //系统时钟48MHZ

input RST_N, //系统复位端

input FROM_AD_DATA, //由AD芯片转化出来的数据

output TO_AD_CS, //输出到AD芯片的片选信号

output TO_AD_CLK, //输出到AD芯片的时钟小于1.1MHZ

output [7:0] DIG, //数码管数字段

output [3:0] SEL //数码管点亮位

);

//*************************************************************************************

wire [7:0] TO_DISPLAY_DATA; //输出到数码管现实模块的数据

//*************************************************************************************

// 调用AD控制模块

//*************************************************************************************

AD_CONTROL_MODULE AD_CONTROL_MODULE1(

.CLK_48M (CLK_48M), //系统时钟48MHZ

.RST_N (RST_N), //系统复位端

.FROM_AD_DATA (FROM_AD_DATA), //由AD芯片转化出来的数据

.TO_AD_CS (TO_AD_CS), //输出到AD芯片的片选信号

.TO_AD_CLK (TO_AD_CLK), //输出到AD芯片的时钟小于1.1MHZ

.TO_DISPLAY_DATA (TO_DISPLAY_DATA) //输出到数码管现实模块的数据

);

//*************************************************************************************

// 调用数码管显示模块

//*************************************************************************************。

DISPLAY_MODULE DISPLAY_MODULE1(

.CLK_48M (CLK_48M), //系统时钟48MHZ

.RST_N (RST_N), //系统复位端

.FROM_AD_CONTRL_DATA (TO_DISPLAY_DATA), //从AD控制模块输入的数据

.DIG (DIG), //数码管数字段

.SEL (SEL) //数码管点亮位

);

//*************************************************************************************

endmodule

分割-----------------------------------------------------------------------------------------------------------------

/*************************************************************************************

* 日期:2016年11月18日22:14:52 *

* 作者:黄志华 *

* 功能:AD控制模块 *

* 修改:2016年11月19日17:31:49 *

*************************************************************************************/

module AD_CONTROL_MODULE(

input CLK_48M, //系统时钟48MHZ

input RST_N, //系统复位端

input FROM_AD_DATA, //由AD芯片转化出来的数据

output reg TO_AD_CS, //输出到AD芯片的片选信号

output reg TO_AD_CLK, //输出到AD芯片的时钟小于1.1MHZ

output reg [7:0] TO_DISPLAY_DATA //输出到数码管现实模块的数据

);

//*************************************************************************************

parameter FSM_WAIT = 5'b00001; //1.5us

parameter FSM_DELAY = 5'b00010; //1/4*2=0.5us

parameter FSM_DATA = 5'b00100; //8*1/1.1=8*0.91us

parameter FSM_OVER = 5'b01000; //17us

parameter FSM_END = 5'b10000; //0.2us

parameter AD_CLK_TIME = 6'd44; //48M/1.1M<44

parameter AD_CLK_TIME_HALF = 6'd22; //一半的1.1MHZ

//*************************************************************************************

reg TO_AD_CS_N; //输出到AD芯片的片选信号

reg TO_AD_CLK_N; //输出到AD芯片的时钟小于1.1MHZ

reg [7:0] TO_DISPLAY_DATA_N; //输出到数码管现实模块的数据

reg [4:0] FSM_REG_CS; //状态机寄存器当前状态

reg [4:0] FSM_REG_NS; //状态机寄存器下一状态

reg [5:0] AD_CLK_TIME_CNT; //AD_CLK周期计数

reg [5:0] AD_CLK_TIME_CNT_N; //AD_CLK周期计数

reg [5:0] AD_CLK_TIME_COUNTER; //AD_CLK计数器

reg [7:0] FROM_AD_DATA_REG; //从接收AD芯片输入的8位数据

reg [7:0] FROM_AD_DATA_REG_N; //从接收AD芯片输入的8位数据

reg [7:0] STEADY_DATA; //从接收AD芯片输入的8位数据稳定的数据

reg [7:0] STEADY_DATA_N; //从接收AD芯片输入的8位数据稳定的数据

//*************************************************************************************

// 有限状态机FSM

//*************************************************************************************

always @(posedge CLK_48M)

begin

if(!RST_N) FSM_REG_CS<=1'b0; //当前状态赋值

else FSM_REG_CS<=FSM_REG_NS;

end

//*************************************************************************************

always @(*)

begin

case(FSM_REG_CS)

FSM_WAIT:begin if((AD_CLK_TIME_CNT==2)&&(AD_CLK_TIME_COUNTER==AD_CLK_TIME))

FSM_REG_NS=FSM_DELAY;

else FSM_REG_NS=FSM_REG_CS; end

FSM_DELAY:begin if((AD_CLK_TIME_CNT==1)&&(AD_CLK_TIME_COUNTER==AD_CLK_TIME))

FSM_REG_NS=FSM_DATA;

else FSM_REG_NS=FSM_REG_CS; end //下个状态赋值

FSM_DATA:begin if((AD_CLK_TIME_CNT==8)&&(AD_CLK_TIME_COUNTER==AD_CLK_TIME))

FSM_REG_NS=FSM_OVER;

else FSM_REG_NS=FSM_REG_CS; end

FSM_OVER:begin if((AD_CLK_TIME_CNT==19)&&(AD_CLK_TIME_COUNTER==AD_CLK_TIME))

FSM_REG_NS=FSM_END;

else FSM_REG_NS=FSM_REG_CS; end

FSM_END:begin if((AD_CLK_TIME_CNT==2)&&(AD_CLK_TIME_COUNTER==AD_CLK_TIME))

FSM_REG_NS=FSM_WAIT;

else FSM_REG_NS=FSM_REG_CS; end

default: FSM_REG_NS=FSM_WAIT;

endcase

end

//*************************************************************************************

// TO_AD_CLK波形生成

//*************************************************************************************

always @(posedge CLK_48M)

begin

if(!RST_N) TO_AD_CLK<=1'b0; //当前状态赋值

else TO_AD_CLK<=TO_AD_CLK_N;

end

//*************************************************************************************

always @(*)

begin

if(FSM_REG_CS!=FSM_DATA) TO_AD_CLK_N=0;

else if(AD_CLK_TIME_COUNTER==AD_CLK_TIME)

TO_AD_CLK_N=1; //下个状态赋值

else if(AD_CLK_TIME_COUNTER==AD_CLK_TIME_HALF)

TO_AD_CLK_N=0;

else TO_AD_CLK_N=TO_AD_CLK;

end

//*************************************************************************************

// TO_AD_CS波形生成

//*************************************************************************************

always @(posedge CLK_48M)

begin

if(!RST_N) TO_AD_CS<=1'b0; //当前状态赋值

else TO_AD_CS<=TO_AD_CS_N;

end

//*************************************************************************************

always @(*)

begin

case(FSM_REG_CS)

FSM_WAIT: TO_AD_CS_N=1;

FSM_DELAY: TO_AD_CS_N=0;

FSM_DATA: TO_AD_CS_N=0; //下个状态赋值

FSM_OVER: TO_AD_CS_N=1;

FSM_END: TO_AD_CS_N=1;

default: TO_AD_CS_N=1;

endcase

end

//*************************************************************************************

// AD_CLK周期计数

//*************************************************************************************

always @(posedge CLK_48M)

begin

if(!RST_N) AD_CLK_TIME_CNT<=1'b0; //当前状态赋值

else AD_CLK_TIME_CNT<=AD_CLK_TIME_CNT_N;

end

//*************************************************************************************

always @(*)

begin

if(FSM_REG_CS!=FSM_REG_NS) AD_CLK_TIME_CNT_N<=0;

else if(AD_CLK_TIME_COUNTER==AD_CLK_TIME_HALF) //下个状态赋值

AD_CLK_TIME_CNT_N=AD_CLK_TIME_CNT+1;

else AD_CLK_TIME_CNT_N=AD_CLK_TIME_CNT;

end

//*************************************************************************************

// 1.1MHZ计数

//*************************************************************************************

always @(posedge CLK_48M)

begin

if(!RST_N) AD_CLK_TIME_COUNTER<=0;

else if(AD_CLK_TIME_COUNTER==AD_CLK_TIME) //下个状态赋值

AD_CLK_TIME_COUNTER<=0;

else AD_CLK_TIME_COUNTER<=AD_CLK_TIME_COUNTER+1'b1;

end

//*************************************************************************************

// 输入数据移位寄存器

//*************************************************************************************

always @(posedge CLK_48M)

begin

if(!RST_N) FROM_AD_DATA_REG<=1'b0; //当前状态赋值

else FROM_AD_DATA_REG<=FROM_AD_DATA_REG_N;

end

//*************************************************************************************

always @(*)

begin //下个状态赋值

if((FSM_REG_CS==FSM_DATA)&&(AD_CLK_TIME_COUNTER==AD_CLK_TIME_COUNTER))

FROM_AD_DATA_REG_N={FROM_AD_DATA_REG[6:0],FROM_AD_DATA};

else FROM_AD_DATA_REG_N=FROM_AD_DATA_REG;

end

//*************************************************************************************

// 稳定输出数据

//*************************************************************************************

always @(posedge CLK_48M)

begin

if(!RST_N) TO_DISPLAY_DATA<=1'b0; //当前状态赋值

else TO_DISPLAY_DATA<=TO_DISPLAY_DATA_N;

end

//*************************************************************************************

always @(*)

begin

if(AD_CLK_TIME_CNT==8) TO_DISPLAY_DATA_N=FROM_AD_DATA_REG;

else TO_DISPLAY_DATA_N=TO_DISPLAY_DATA;

end

//*************************************************************************************

endmodule

分割-----------------------------------------------------------------------------------------------------------------

/*************************************************************************************

* 日期:2016年11月18日22:14:52 *

* 作者:黄志华 *

* 功能:数码管显示模块 *

* 修改:2016年11月19日17:54:19 *

*************************************************************************************/

module DISPLAY_MODULE(

input CLK_48M, //系统时钟48MHZ

input RST_N, //系统复位端

input [7:0] FROM_AD_CONTRL_DATA, //从AD控制模块输入的数据

output reg [7:0] DIG, //数码管数字段

output reg [3:0] SEL //数码管点亮位

);

//************************************************************************************

parameter Numb0 = 7'b1000000;

parameter Numb1 = 7'b1111001;

parameter Numb2 = 7'b0100100;

parameter Numb3 = 7'b0110000;

parameter Numb4 = 7'b0011001; //数码管显示无点数字定义

parameter Numb5 = 7'b0010010;

parameter Numb6 = 7'b0000010;

parameter Numb7 = 7'b1111000;

parameter Numb8 = 7'b0000000;

parameter Numb9 = 7'b0010000;

//************************************************************************************

parameter SET_SEL0 = 4'b0111;

parameter SET_SEL1 = 4'b1011;

parameter SET_SEL2 = 4'b1101; //数码管分段点亮参数

parameter SET_SEL3 = 4'b1110;

//************************************************************************************

parameter FSM_1 = 1'b0; //状态1

parameter FSM_2 = 1'b1; //状态2

parameter COUNTER = 20'd100_000; //1/48*1000_000=20ms

//************************************************************************************

reg FSM_CS; //状态寄存器当前状态

reg FSM_NS; //状态寄存器下一状态

reg [1:0] TIME_COUNTER; //20ms计数器

reg [6:0] n1; //数码管显示整数部分寄存器

reg [6:0] n2; //数码管显示小数部分寄存器

//************************************************************************************

// 有限状态机FSM

//************************************************************************************

always @(posedge CLK_48M)

begin

if(!RST_N) FSM_CS<=1'b0;

else FSM_CS<=FSM_NS;

end

//************************************************************************************

always @(*)

begin

if(TIME_COUNTER==COUNTER) FSM_NS=FSM_CS+1'b1;

else FSM_NS=FSM_CS;

end

//************************************************************************************

// 显示设置

//************************************************************************************

always @(*)

begin

case(FSM_CS)

FSM_1:begin DIG[6:0]=n1;DIG[7]=1'b0;SEL=SET_SEL0; end

FSM_2:begin DIG[6:0]=n2;DIG[7]=1'b1;SEL=SET_SEL1; end

default:SEL=4'b1111;

endcase

end

//************************************************************************************

// 20ms计时

//************************************************************************************

always @(posedge CLK_48M)

begin

if(!RST_N) TIME_COUNTER<=1'b0;

else if(TIME_COUNTER==COUNTER)

TIME_COUNTER<=1'b0;

else TIME_COUNTER<=TIME_COUNTER+1'b1;

end

//************************************************************************************

// 数据转换

//************************************************************************************

always @(*)

begin

case(FROM_AD_CONTRL_DATA[7:2])

6'd0:begin n1=Numb0;n2=Numb0;end

6'd1:begin n1=Numb0;n2=Numb1;end

6'd2:begin n1=Numb0;n2=Numb1;end

6'd3:begin n1=Numb0;n2=Numb2;end

6'd4:begin n1=Numb0;n2=Numb2;end

6'd5:begin n1=Numb0;n2=Numb3;end

6'd6:begin n1=Numb0;n2=Numb3;end

6'd7:begin n1=Numb0;n2=Numb4;end

6'd8:begin n1=Numb0;n2=Numb4;end

6'd9:begin n1=Numb0;n2=Numb5;end

6'd10:begin n1=Numb0;n2=Numb5;end

6'd11:begin n1=Numb0;n2=Numb6;end

6'd12:begin n1=Numb0;n2=Numb6;end

6'd13:begin n1=Numb0;n2=Numb7;end

6'd14:begin n1=Numb0;n2=Numb7;end

6'd15:begin n1=Numb0;n2=Numb8;end

6'd16:begin n1=Numb0;n2=Numb8;end

6'd17:begin n1=Numb0;n2=Numb9;end

6'd18:begin n1=Numb0;n2=Numb9;end

6'd19:begin n1=Numb1;n2=Numb0;end

6'd20:begin n1=Numb1;n2=Numb0;end

6'd21:begin n1=Numb1;n2=Numb1;end

6'd22:begin n1=Numb1;n2=Numb1;end

6'd23:begin n1=Numb1;n2=Numb2;end

6'd24:begin n1=Numb1;n2=Numb2;end

6'd25:begin n1=Numb1;n2=Numb3;end

6'd26:begin n1=Numb1;n2=Numb3;end

6'd27:begin n1=Numb1;n2=Numb4;end

6'd28:begin n1=Numb1;n2=Numb4;end

6'd29:begin n1=Numb1;n2=Numb5;end

6'd30:begin n1=Numb1;n2=Numb5;end

6'd31:begin n1=Numb1;n2=Numb6;end

6'd32:begin n1=Numb1;n2=Numb6;end

6'd33:begin n1=Numb1;n2=Numb7;end

6'd34:begin n1=Numb1;n2=Numb7;end

6'd35:begin n1=Numb1;n2=Numb8;end

6'd36:begin n1=Numb1;n2=Numb8;end

6'd37:begin n1=Numb1;n2=Numb9;end

6'd38:begin n1=Numb1;n2=Numb9;end

6'd39:begin n1=Numb2;n2=Numb0;end

6'd40:begin n1=Numb2;n2=Numb0;end

6'd41:begin n1=Numb2;n2=Numb1;end

6'd42:begin n1=Numb2;n2=Numb1;end

6'd43:begin n1=Numb2;n2=Numb2;end

6'd44:begin n1=Numb2;n2=Numb2;end

6'd45:begin n1=Numb2;n2=Numb3;end

6'd46:begin n1=Numb2;n2=Numb3;end

6'd47:begin n1=Numb2;n2=Numb4;end

6'd48:begin n1=Numb2;n2=Numb4;end

6'd49:begin n1=Numb2;n2=Numb5;end

6'd50:begin n1=Numb2;n2=Numb5;end

6'd51:begin n1=Numb2;n2=Numb6;end

6'd52:begin n1=Numb2;n2=Numb6;end

6'd53:begin n1=Numb2;n2=Numb7;end

6'd54:begin n1=Numb2;n2=Numb7;end

6'd55:begin n1=Numb2;n2=Numb8;end

6'd56:begin n1=Numb2;n2=Numb8;end

6'd57:begin n1=Numb2;n2=Numb9;end

6'd58:begin n1=Numb2;n2=Numb9;end

6'd59:begin n1=Numb3;n2=Numb0;end

6'd60:begin n1=Numb3;n2=Numb0;end

6'd61:begin n1=Numb3;n2=Numb1;end

6'd62:begin n1=Numb3;n2=Numb1;end

6'd63:begin n1=Numb3;n2=Numb2;end

default:SEL=4'b1111;

endcase

end

//************************************************************************************

endmodule

来人呐~~~~数码管都是低电平有效~~

程序太长没细看,你可以看一下如果只是第一个数码管显示”6“,那么很有可能是数码管扫描显示的时候,扫描过程出现问题了,导致停在第一个数码管上了,你仔细看看吧- -

啊啊啊啊啊啊啊啊啊啊啊啊啊啊啊啊啊