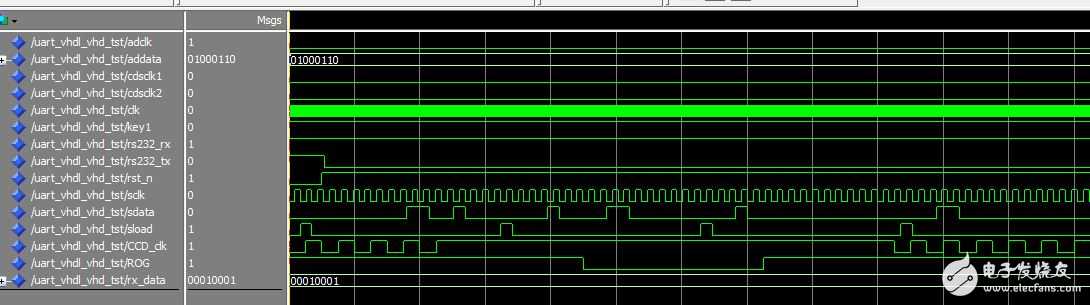

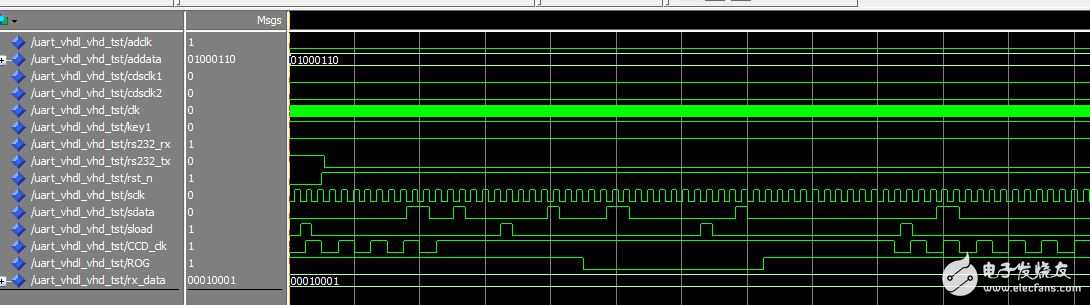

FPGA时序波形测出来好奇怪!

用示波器测出来的是这样的:

我的问题是,为什么方波看起来不那么方,而且还有刺。

我的几个猜测:1 实验室的示波器比较渣,所以测不出来

2 时序频率太高了,FPGA已经Hold不住了,应该降低频率

请有经验的同志们帮我看看可能是什么原因。在此献出我的积分了。

你的示波器的采样频率最高能到多少 ?如果超过2M的话,那么采样1M的时钟应该没有问题。

个人感觉跟FPGA无关,应该属于FPGA管脚上电平驱动测试引脚的时候,模拟部分的阻抗不匹配所致,示波器的接地端接地情况也好好看看,接地不良也有可能出问题。

示波器不好,或者接地没接好。

不错哟

泰克示波器怎么会渣?

会不会是干扰或者电路设计的不好导致的?

应该是电路的问题把

示波器采样率低了,这种泰科的示波器迷你对纳秒级的测量均有这样的问题

有点高大上的感觉觉!

你阻抗匹配吗?

很正常啊,实际和理想当然有差距,方波的意义在于高低电平,逻辑电路的本质在于满足建立保持时间,又不是模拟电路,不要过分在意波形,只要大于阈值电压,毛刺怎么拐是没有影响的

应该是输出阻尼不足而导致的过冲现象。可以尝试在输出口加一电容电阻增加阻尼削掉尖峰。但如果电容太大阻尼太大的话又会导致方波坡度不够,变成圆角的方波。要选择适当。

同意11楼的说法,方波测出这个样子实际上算是一般的(不算太差),很多实际应用的电路的,时序波形比这个变形得更严重都能正常工作,当然如果能在时序端做好阻抗匹配,会降低方波的过冲,得出的波形也更好看。

输出端接10k电阻下拉,重新测试即可,波形会规整很多。

通过波形可以看出,FPGA输出端应该是开路输出,应该添加上拉或者下拉电阻后测试才可以!

问题已经解决,谢谢大家的回答。奖励分给写的最多的通知了。

下面是现在的波形图,已经改观很多。原因在于示波器的表笔,有一个表笔比较旧了,只要用那个测图像就会莫名其妙的扭曲,可能是因为那个烂表笔阻抗不匹配了吧,在实验室翻箱倒柜用上了崭新的表笔。图像能看了。另外沙发说的也很有道理啊,开始作死搞了一个20MHz的时钟,用示波器根本就测不出方波嘛,超过采样频率了。

总之谢谢大家啦。

你的VHDL程序还有吗