新手想把4位乘法器扩展成8位的,然后遇到了问题。

顺便,我这样写能实现功能吗,不能仿真我也不知道自己写的对不对。如果不对的话,要怎么扩展呢?

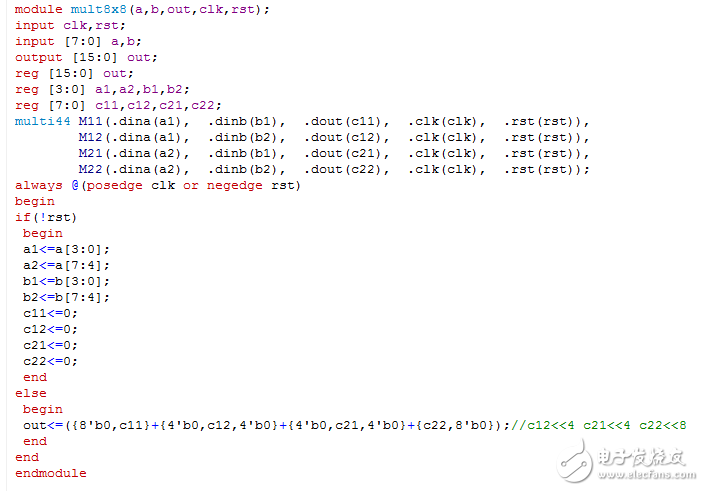

给你个代码,我自己写的。8位的乘法器,可以自己去仿真看看。

module mul_ser(

Clk,

Rst_n,

x0,

x1,

y

);

input Clk;

input Rst_n;

input [7:0]x0;

input [7:0]x1;

output reg [15:0]y;

reg [7:0]t;

reg [15:0]p;

reg [7:0]count;

reg [3:0]state;

always @ (posedge Clk or negedge Rst_n)

begin

if(!Rst_n)

begin

state = 8'd8)

state = count)

state <= 4'd1;

else

begin

state <= 4'd2;

t <= t + 1'b1;

p <= p<<1;

end

end

4'd3:

begin

//y <= p;

end

endcase

end

end

//always @ (posedge Clk or negedge Rst_n)

//begin

// if(!Rst_n)

// begin

// y <= 16'd0;

// end

// else

// y <= x0*x1;

//end

endmodule

有很多该删的,我懒的删,就这样了,你自己看看。

谢谢